### Master's Thesis Nr. 118

Systems Group, Department of Computer Science, ETH Zurich

# Message Passing and Bulk Transport on Heterogeneous Multiprocessors

by

Reto Achermann

Supervised by

Prof. Timothy Roscoe, Dr. Kornilios Kourtis

October 17, 2014

### Abstract

The decade of symmetric multiprocessors is about to end. Due to physical limitations, individual cores cannot be made any faster and adding cores won't work anymore (dark silicon). Operating systems face the next big paradigm shift: systems are getting faster by exploiting specialized hardware leading to the era of asymmetric processors and heterogeneous systems. An ever growing count and the diversity of cores yields new challenges regarding scheduling and resource management. Multiple physical address spaces within single machines let them appear as a cluster-like system.

Today's commodity operating systems are not well designed to deal with heterogeneity and asymmetric processors. Many attempts have been made to tackle the challenges of heterogeneous hardware, most of which treat available co-processors like devices or independent execution environments rather than equivalent processors. Thus, true support of a multi-architecture system is rarely seen, despite the fact that such hardware already exists. Examples are, systems like the OMAP44xx SoC or Intel's Xeon Phi co-processor.

In this thesis we will elaborate the arising challenges introduced by heterogeneous system architectures. We ported the Barrelfish research operating system to the Xeon Phi execution environment and explored the impact on performance and system design imposed by the emerging hardware characteristics such as different instruction set architectures, multiple physical address spaces and asymmetric cores. Based on our proposed software framework, we demonstrate a parallel, heterogeneous execution of an OpenMP program using our implementation of a message passing based OpenMP library and show why more threads do not necessary imply a better performance.

# Acknowledgments

I want to thank Prof. Timothy Roscoe for giving me the opportunity to work with the new Xeon Phi hardware and for his inspirational thoughts and critical questions during our discussions; Dr. Kornilios Kourtis for his feedback on the benchmarks and Stefan Kaestle for his ideas about possible applications. Further, I'd like to thank Raphael Fuchs for the inspirational discussions about Barrelfish.

# Contents

| 1 | $\mathbf{Intr}$   | oduction and Motivation                                      | 9                                |

|---|-------------------|--------------------------------------------------------------|----------------------------------|

| 2 | 2.1<br>2.2<br>2.3 | Intel Manycore Platform Software Stack Heterogeneous Systems | 12<br>13<br>13<br>13<br>14<br>15 |

|   | 2.4               |                                                              | 16                               |

| 3 | Bar               |                                                              | 17                               |

|   | 3.1               |                                                              | 17<br>18                         |

|   | 3.2               |                                                              | 18                               |

|   | 3.3               | 1                                                            | $\frac{10}{19}$                  |

|   |                   | v                                                            | 19                               |

|   |                   |                                                              | 19                               |

|   |                   |                                                              | 19                               |

|   |                   | 3.3.4 Device Drivers                                         | 20                               |

|   | 3.4               | Message Passing                                              | 20                               |

|   |                   | 1 0                                                          | 20                               |

|   |                   | 0                                                            | 20                               |

|   | 3.5               | 8                                                            | 21                               |

|   | 3.6               | ·                                                            | 21                               |

|   |                   | 3.6.1 Hakefiles                                              | 21                               |

| 4 | The               | Intel Xeon Phi Co-Processor                                  | 22                               |

|   | 4.1               |                                                              | 23                               |

|   | 4.2               |                                                              | 23                               |

|   |                   |                                                              | 24                               |

|   |                   |                                                              | 24                               |

|   |                   | 4.2.3 Comparison to General Purpose GPUs                     | 25                               |

|   | 4.3               | V 1 V                                                        | 26                               |

|   |                   |                                                              | 26                               |

|   |                   |                                                              | 27                               |

|   |                   | 4.3.3 Multiple Physical Address Spaces                       | 27                               |

CONTENTS 4

|   |     | 4.3.4         | Accessing Resources of another Processor |   |   |       |       |   | 29              |

|---|-----|---------------|------------------------------------------|---|---|-------|-------|---|-----------------|

|   | 4.4 | The K         | 10M Architecture                         |   |   |       |       |   | 29              |

|   | 4.5 | Bootin        | ng the Xeon Phi                          |   |   |       |       |   | 31              |

|   |     | 4.5.1         | Operating Systems                        |   |   |       |       |   | 31              |

|   |     | 4.5.2         | Bootstrap                                |   |   |       |       |   | 31              |

|   |     | 4.5.3         | Boot Modes                               |   |   |       |       |   | 32              |

| 5 | Mei | mory /        | Access over PCI Express                  |   |   |       |       |   | 33              |

| J | 5.1 |               | ry Hierarchy                             |   |   |       |       |   | 33              |

|   | 0.1 | 5.1.1         | Memory Access with Co-Processors         |   |   |       |       |   | 34              |

|   | 5.2 |               | ating Memory Access Performance          |   |   |       |       |   | 35              |

|   | 5.3 |               | ry Access Latency                        |   |   |       |       |   | 35              |

|   | 0.0 | 5.3.1         | Benchmark Description                    |   |   |       |       |   | 35              |

|   |     | 5.3.2         | Benchmark Results                        |   |   |       |       |   | 36              |

|   |     | 5.3.2         | Implications                             |   |   |       |       |   | 38              |

|   | 5.4 |               | ry Throughput                            |   |   |       |       |   | 39              |

|   | 0.4 | 5.4.1         | Benchmark Description                    |   |   |       |       |   | 39              |

|   |     | 5.4.2         | Benchmark Baseline: Local Transfers      |   |   |       |       |   | 39              |

|   |     | 5.4.2 $5.4.3$ | Host to Xeon Phi Transfers               |   |   |       |       |   | 41              |

|   |     | 5.4.4         | Xeon Phi to Host Transfers               |   |   |       |       |   | 43              |

|   |     | 5.4.4 $5.4.5$ | Between Xeon Phi                         |   |   |       |       |   | 43              |

|   |     | 5.4.6         |                                          |   |   |       |       |   | 43              |

|   | 5.5 |               | Implications                             |   |   |       |       |   | $\frac{43}{44}$ |

|   | 5.5 | 5.5.1         | Benchmark Description                    |   |   |       |       |   | 44              |

|   |     |               |                                          |   |   |       |       |   | 44              |

|   |     | 5.5.2         | Benchmark Baseline: Local Benchmark .    |   |   |       |       |   |                 |

|   |     | 5.5.3         | Message Passing over PCI Express         |   |   |       |       |   | 46              |

|   | F C | 5.5.4         | Implications                             |   |   |       |       |   | 48              |

|   | 5.6 | A WOI         | rd on CPU Performance                    | ٠ | • | <br>• | <br>• | • | 48              |

| 6 |     |               | on the Xeon Phi                          |   |   |       |       |   | <b>50</b>       |

|   | 6.1 |               | n Overview                               |   |   |       |       |   | 50              |

|   |     | 6.1.1         | Xeon Phi Driver                          |   |   |       |       |   | 51              |

|   |     | 6.1.2         | Xeon Phi Manager                         |   |   |       |       |   | 52              |

|   |     | 6.1.3         | Service and Domain Identification        |   |   |       |       |   | 53              |

|   | 6.2 |               | ences and Similarities to the MPSS       |   |   |       |       |   | 54              |

|   | 6.3 |               | ications to Barrelfish                   |   |   |       |       |   | 54              |

|   |     | 6.3.1         | Boot-Loader                              |   |   |       |       |   | 54              |

|   |     | 6.3.2         | CPU Driver and Monitor                   |   |   |       |       |   | 54              |

|   |     | 6.3.3         | Kaluga and SKB                           |   |   |       |       |   | 55              |

|   | 6.4 | Creati        | ng the Xeon Phi Bootimage                |   |   |       |       |   | 56              |

|   |     | 6.4.1         | Additional Hake Targets                  |   |   |       |       |   | 56              |

|   |     | 6.4.2         | Boot-Image Anatomy                       |   |   |       |       |   | 56              |

|   |     | 6.4.3         | Building Process                         |   |   |       |       |   | 57              |

|   | 6.5 | The B         | oot Process Explained                    |   |   |       |       |   | 58              |

|   |     | 6.5.1         | Boot Dependencies                        |   |   |       |       |   | 58              |

|   |     | 6.5.2         | Host Side Driver Startup                 |   |   |       |       |   | 58              |

|   |     | 6.5.3         | Chain of Boot Events                     |   |   |       |       |   | 59              |

|   |     | 6.5.4         | Weever: The Xeon Phi Boot-Loader         |   |   |       |       |   | 60              |

|   | 6.6 | Capab         | oilities Revisited                       |   |   |       |       |   | 61              |

|   |     | 6.6.1         | The Problem of Multiple Address Spaces   |   |   |       |       |   | 61              |

CONTENTS 5

| $\mathbf{A}_{\mathbf{I}}$ | ppen | dices      |                                           |   |   |   |   |   | 110 |

|---------------------------|------|------------|-------------------------------------------|---|---|---|---|---|-----|

|                           | 0.11 | VII 01 O . |                                           | • | • | • | • | • | 109 |

|                           |      |            |                                           |   |   |   |   |   |     |

|                           |      |            | Hardware Features                         |   |   |   |   |   |     |

|                           | 8.9  |            | nsport over PCI Express                   |   |   |   |   |   |     |

|                           | 8.8  |            |                                           |   |   |   |   |   |     |

|                           | 8.7  |            | rary                                      |   |   |   |   |   |     |

|                           | 8.6  |            | g Flounder                                |   |   |   |   |   |     |

|                           | 8.5  |            | ng to the Xeon Phi and Host VFS           |   |   |   |   |   |     |

|                           | 8.4  |            | : Explore Scaling Behavior                |   |   |   |   |   |     |

|                           | 8.3  |            | Address Spaces                            |   |   |   |   |   |     |

|                           | 8.2  |            | as a Collection of Cores                  |   |   |   |   |   |     |

|                           | 8.1  |            | One System                                |   |   |   |   |   | 102 |

| 8                         | Futi | ıre Work   |                                           |   |   |   |   |   | 102 |

|                           | 7.4  | Conclusio  | n                                         |   |   |   |   | • | 100 |

|                           |      |            | atrix Multiply using Heterogeneous OpenMP |   |   |   |   |   |     |

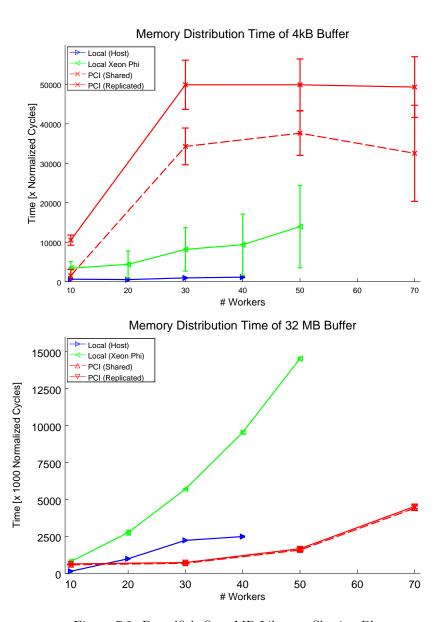

|                           |      |            | fect of Data Replication                  |   |   |   |   |   |     |

|                           |      |            | aseline: Local Benchmarks                 |   |   |   |   |   |     |

|                           |      |            | eneral Benchmark Description              |   |   |   |   |   |     |

|                           | 7.3  |            | Example: Matrix Multiplication            |   |   |   |   |   |     |

|                           | _    |            | brary Scaling Characteristics             |   |   |   |   |   |     |

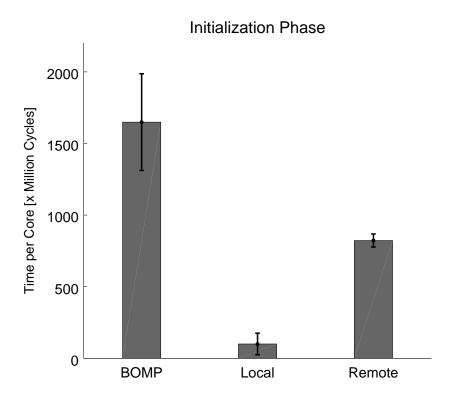

|                           |      |            | brary Initialization                      |   |   |   |   |   |     |

|                           |      |            | OMP: OpenMP for Exclusive Address Spaces  |   |   |   |   |   |     |

|                           |      |            | OMP: Barrelfish OpenMP                    |   |   |   |   |   |     |

|                           |      |            | omputation Model                          |   |   |   |   |   |     |

|                           | 7.2  | -          |                                           |   |   |   |   |   |     |

|                           | _    |            | equirements for Offloading                |   |   |   |   |   |     |

|                           | 7.1  |            | oading                                    |   |   |   |   |   |     |

| 7                         |      | lications  | 1.                                        |   |   |   |   |   | 83  |

|                           |      |            |                                           | • | • |   | • | • |     |

|                           |      |            | rtual Devices: A Conclusion               |   |   |   |   |   |     |

|                           |      |            | arrelfish Bulk Transport                  |   |   |   |   |   |     |

|                           |      |            | rtIO                                      |   |   |   |   |   |     |

|                           | 6.10 |            | evices                                    |   |   |   |   |   |     |

|                           |      |            | MA Subsystem Programming Model            |   |   |   |   |   |     |

|                           |      |            | MA Manager                                |   |   |   |   |   |     |

|                           | -    |            | MA Library                                |   |   |   |   |   |     |

|                           | 6.9  |            | vice                                      |   |   |   |   |   |     |

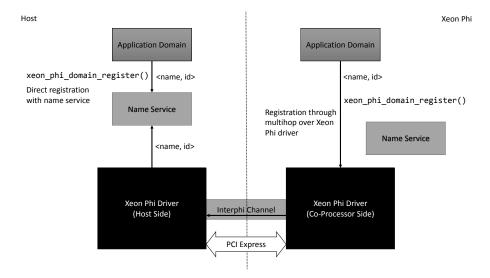

|                           |      |            | ame Services                              |   |   |   |   |   |     |

|                           |      |            | eon Phi Driver Service                    |   |   |   |   |   |     |

|                           | 6.8  |            | Service Interfaces                        |   |   |   |   |   |     |

|                           |      |            | mitations                                 |   |   |   |   |   |     |

|                           |      |            | sage                                      |   |   |   |   |   |     |

|                           |      |            | essage Stub Interface Extensions          |   |   |   |   |   |     |

|                           |      |            | bunder Bootstrap Steps                    |   |   |   |   |   |     |

|                           | 6.7  |            | over PCI Express                          |   |   |   |   |   |     |

|                           |      |            | apability Translation: An Implementation  |   |   |   |   |   |     |

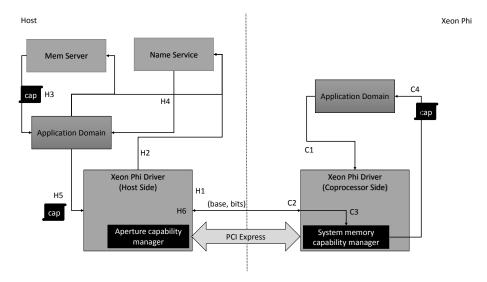

|                           |      | 6.6.2 Ca   | apabilities: Accessing Remote Resources   |   |   |   |   |   | 62  |

CONTENTS 6

| A            | Mer | nory Access Benchmarks 1         | 11  |

|--------------|-----|----------------------------------|-----|

|              | A.1 | Xeon Phi Caches                  | 111 |

|              | A.2 | Memory Latency                   | 111 |

|              |     | A.2.1 Experiment Description     |     |

|              |     | A.2.2 Experiment Parameters      | 112 |

|              | A.3 | Memory Throughput                |     |

|              |     | A.3.1 Experiment Description     | 113 |

|              |     | A.3.2 Experiment Parameters      | 113 |

|              | A.4 | Memcopy Closeup                  | 113 |

|              | A.5 | DMA Driver Overhead              | 114 |

|              | A.6 | Message Passing                  | 115 |

|              |     | A.6.1 Experiment Description     | 115 |

|              |     | A.6.2 Experiment Parameters      | 115 |

|              |     | A.6.3 UMP Latency Distribution   | 116 |

| В            | Оре | enMP Benchmark                   | 18  |

|              | В.1 | Library Initialization           | 118 |

|              |     | Matrix Multiplication            |     |

| $\mathbf{C}$ | Bar | relfish 1                        | 21  |

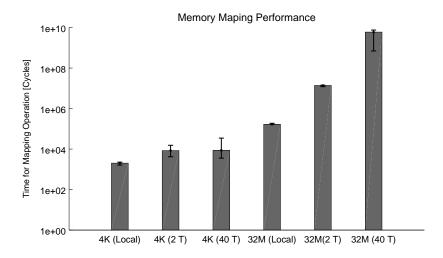

|              | C.1 | Memory Mapping in Barrelfish     | 121 |

|              |     | C.1.1 Benchmark Discussion       |     |

|              |     | C.1.2 Side Effects               |     |

|              |     | C.1.3 Conclusions                |     |

|              | C.2 | Boot Performance                 |     |

|              | C.3 | Querying and Registering Symbols |     |

|              |     | C.3.1 Interface Specification    |     |

# List of Figures

| 3.1 | Barrelfish Architecture                                      | 18  |

|-----|--------------------------------------------------------------|-----|

| 4.1 | System Overview with Xeon Phi                                | 24  |

| 4.2 | Address Space Layout of a System with Xeon Phi Co-Processors | 26  |

| 5.1 | The New Memory Hierarchy                                     | 34  |

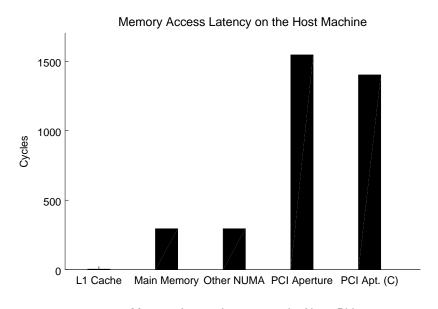

| 5.2 | Memory Access Latencies on Host (top) and Xeon Phi (bottom)  | 37  |

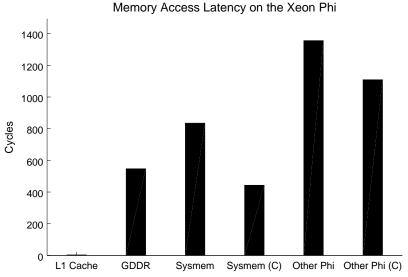

| 5.3 | Memory Throughput on Local Memory                            | 40  |

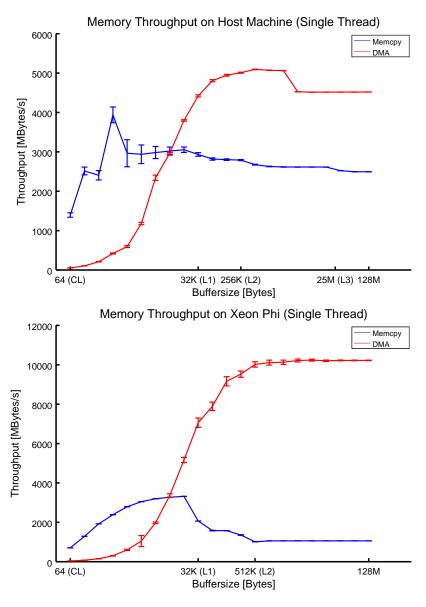

| 5.4 | Memory Transfer from Host to Xeon Phi                        | 42  |

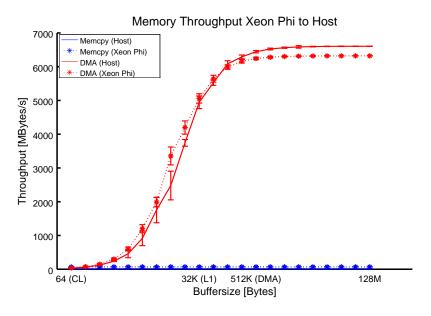

| 5.5 | Memory Transfer from Xeon Phi to Host                        | 42  |

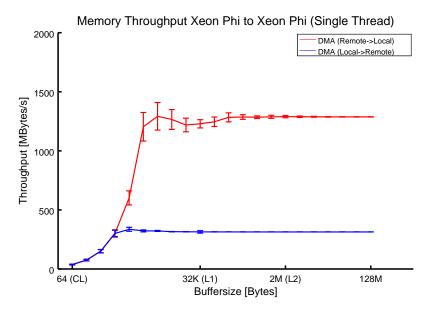

| 5.6 | Memory Throughput Xeon Phi to Xeon Phi                       | 44  |

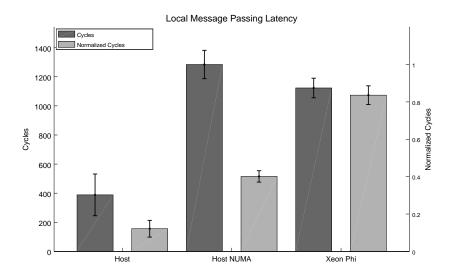

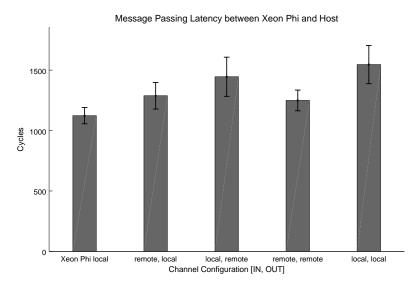

| 5.7 | Message Passing Latency                                      | 45  |

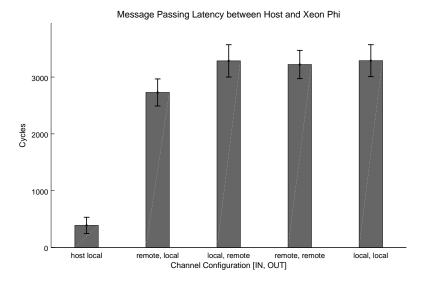

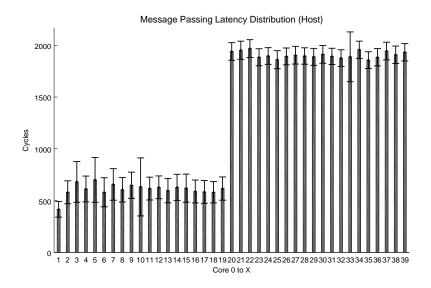

| 5.8 | Message Passing Latency over PCI Express (Host)              | 46  |

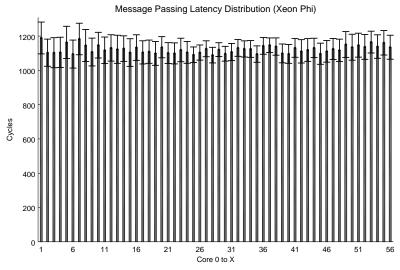

| 5.9 | Message Passing Latency over PCI Express (Xeon Phi)          | 47  |

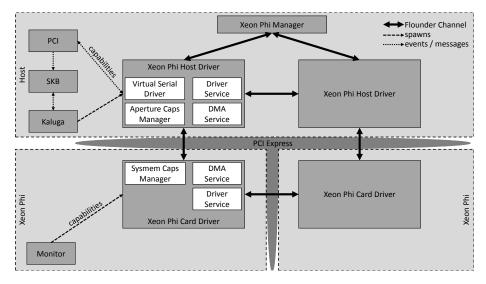

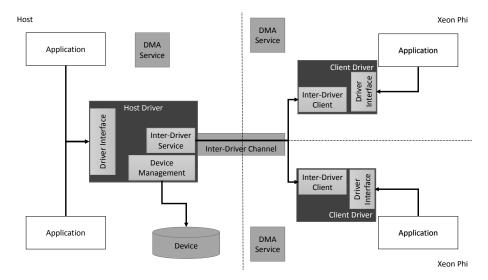

| 6.1 | Software System Overview                                     | 51  |

| 6.2 | Transferring of Capabilities between Address Spaces          | 63  |

| 6.3 | Xeon Phi Name Service                                        | 72  |

| 6.4 | Emulating Virtual Devices on Co-Processors                   | 78  |

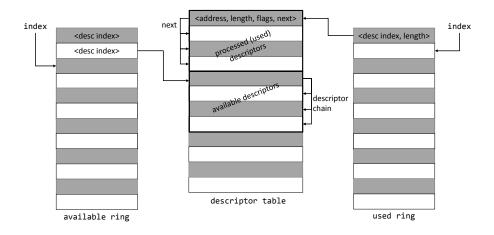

| 6.5 | VirtIO: Virtqueue Operation Scheme                           | 79  |

| 7.1 | Barrelfish OpenMP Library: Initialization Phase Spawn Time   | 92  |

| 7.2 | Barrelfish OpenMP Library: Sharing Phase                     | 94  |

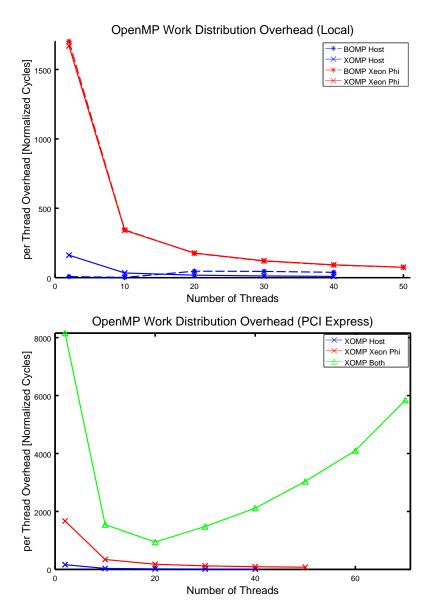

| 7.3 | Barrelfish OpenMP Library: Work Distribution                 | 96  |

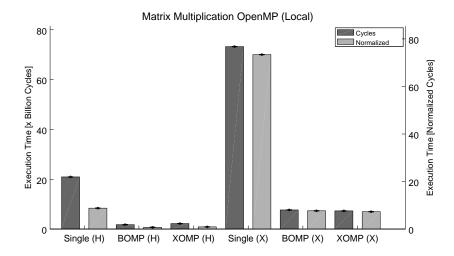

| 7.4 | Local Matrix Multiplication using OpenMP                     | 98  |

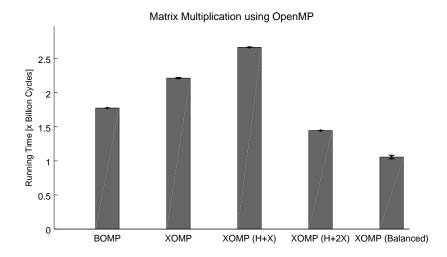

| 7.5 | Matrix Multiplication on Heterogeneous System using OpenMP   | 99  |

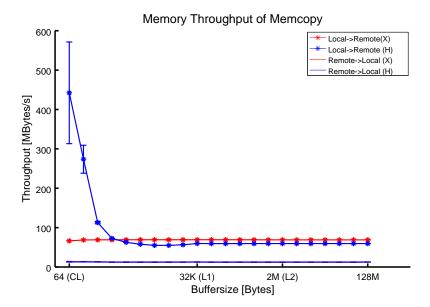

| A.1 | Memcopy Throughput                                           | 114 |

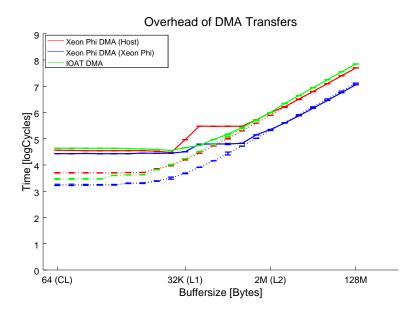

| A.2 | DMA Driver Overhead                                          | 115 |

| A.3 | UMP Latency Distribution                                     | 117 |

| C.1 | Memory Mapping Performance with Multiple Domains             | 122 |

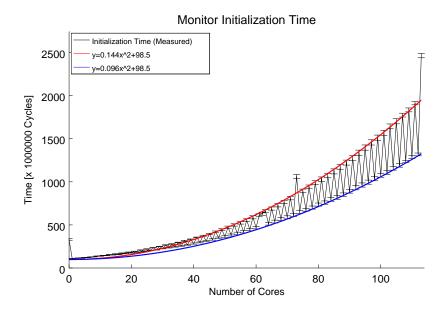

| C.2 | Initialization Time per Monitor                              | 123 |

# List of Tables

| 4.1 | Xeon Phi Historic Overview                               | 22 |

|-----|----------------------------------------------------------|----|

| 4.2 | System Description                                       | 23 |

| 4.3 | Xeon Phi Hardware Specification                          |    |

| 4.4 | Special Header Bytes                                     | 32 |

| 5.1 | Memory Access Latencies                                  | 36 |

| 5.2 | Local Message Passing Latencies (RTT)                    | 45 |

| 5.3 | Integer Performance in Millions of Operations per Second | 48 |

| 6.1 | Xeon Phi Domain ID Bit Representation                    | 53 |

| 7.1 | Barrelfish OpenMP Library: Work Distribution (Local)     | 95 |

| 7.2 | OpenMP Matrix Multiplication Settings                    | 97 |

| 7.3 | OpenMP Matrix Multiplication Local Parallelization       | 97 |

| A.1 | Experiment Parameters: Memory Access Latency             | 13 |

| A.2 | Experiment Parameters: Memory Throughput                 | 13 |

| A.3 | Experiment Parameters: UMP Latency                       | 15 |

### Chapter 1

# Introduction and Motivation

Today's computer systems are getting increasingly complex. Gordon Moore in [54] formulated the prediction that the number of components per dense integrated circuit doubles approximately every two years. The ever increasing number of transistors on a chip together with an ever increasing clock frequency led to very complex and power hungry designs which certainly hit the so-called power wall [66].

Reaching the physical limits of heat dissipation, clock frequency could no longer be doubled every 18 month. As Moore's law still applies, the number of transistors per CPU keeps increasing whereas clock frequency stagnated or even decreased. To overcome the facing plateau of CPU performance chip designer embedded multiple cores onto a single die starting the multi-core era. This ended the *free lunch* [77], in other words, software was no longer getting faster automatically with every new generation: engineers needed to adapt for the new multi processing principles. Today's modern server processor have 10 cores or more.

The offered parallelism is even more increased by putting multiple CPUs in a single system resulting in a NUMAchine [33]. Besides the challenges of using parallelism provided by the cores, software engineers also needed to be aware of where to place the buffers to avoid over-saturation of the memory controllers and the inter-connect. Accessing memory is no longer uniform turning the machine into a distributed system [10].

Specialized hardware accelerators such as video cards were used from the early days on, executing certain task more efficient than general purpose CPUs. Accelerators evolved into sophisticated computation devices supporting a more general purpose compute model. With massive amounts of available cores, coprocessors such as Intel's Xeon Phi or nVidia's Tesla provide specialized hardware features for highly parallel workloads in high performance computing.

Still, most of the computation is executed on general purpose processors. With an ever increasing number of transistors per chip and consequently a growing number of cores, the execution performance of scalar code is expected to stagnate. Single threaded programs do no longer run significantly faster with a new CPU generation and the effects are even amplified by the fact that not all code can be parallelized. Technologies such as Intel's TurboBoost [24] try to provide extra compute power for a single core when the other cores are idle. Based on the observation that all cores in today's CPUs are identical, we can infer that it is likely to hit another power wall. Hence, we are facing the end of the multiprocessor decade transitioning to the era of specialized hardware [29]. Offloading certain parts of a computation or even whole processes to co-processors can lead to an overall more efficient computation in terms of response time, throughput or energy consumption.

Today, the demand for energy efficient processors for mobile computing applications or data centers, buzzword  $Green\ Computing\ [35]$ , drives the development of specialized hardware. The potential reduction of the overall energy consumption using specialized hardware enables prolonging battery life and reducing the operation costs of data centers.

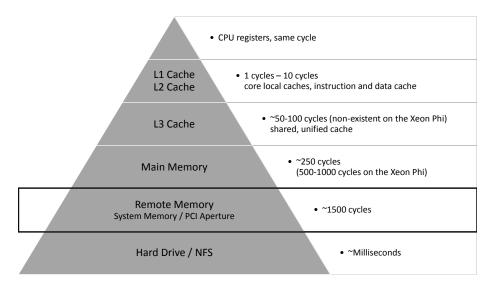

To sum up, hardware is ever changing, offering new challenges to systems developers to make use of the specialized hardware devices. Further, with coprocessors offering massive parallelism, a single machine tends to appear like a high performance cluster. Operating systems have to deal with the additional complexity in terms of number and features of cores, accelerators, co-processors and an overall heterogeneous system architecture. If various architectures are used concurrently, the OS has to be aware of which code can run in which execution environment and where it is expected to run most efficiently. Moreover, traditional abstractions are no longer appropriate for heterogeneous systems: multiple address space layouts, architectures and compute capabilities require new ideas in memory management and scheduling. Additionally, programmers must be aware of a changing memory hierarchy and its implications on execution performance.

This massive amount of parallelism and heterogeneity reveals new questions such as how to manage the resources, how to deal with the different architectures present and how to enable communication of processes running on different architectures?

This thesis will investigate the performance characteristics of the Intel Xeon Phi co-processor and list potential implications towards the design of a system. The proposed software system to manage the heterogeneity forms the basis to show various aspects of such a system and its challenges that need to be solved. Besides, we will present a way to parallelize a program and run across the heterogeneous architectures of a system with Intel Xeon Phi co-processors based on OpenMP.

### Thesis Outline

We structure the thesis in eight chapters, starting off with a survey of related work (Chapter 2) followed by a brief description of Barrelfish the operating system used in this thesis (Chapter 3). The next two chapters describe the hardware features of the Xeon Phi (Chapter 4) and a basic performance evaluation of them (Chapter 5). Based on the insights of the performance characteristics, we present a software system for the Xeon Phi (Chapter 6) and potential applications and use cases (Chapter 7). We list discovered issues and possible anchor points for future work in Chapter 8.

### Terminology

To clarify the technical terms used throughout this thesis, the following list defines how we use the terms to avoid misunderstandings.

- Accelerator Hardware device designed to execute a specific task, decoding audio streams for instance.

- Co-Processor Hardware device designed to execute a wide variety of tasks, a general purpose execution environment. For instance the Xeon Phi or general purpose GPUs. Not to be confused with co-processors like CP15 that controls MMU.

- Host Execution environment which manages the possible co-processors. In our case x86\_64 architecture.

- (Compute) Node Either the Xeon Phi or the host. A system has a single host and may have multiple co-processor nodes.

- Local Memory Main memory of the node. On the Xeon Phi the GDDR, on the host the RAM.

- Remote Memory From the Xeon Phi point of view referring to the system memory or the GDDR of another Xeon Phi. Viewed from the host, the Xeon Phi aperture space.

- Thread/Worker In the OpenMP context, thread and worker (domains) can be used interchangeably.

- Client Driver Instance of a driver running on the co-processor connected to its counterpart on the host.

### Chapter 2

### Related Work

Heterogeneous system in a broader sense exists since the early days, ranging from specialized micro-controllers for digital signal processing to graphic accelerators (video cards). However, despite their heterogeneity, operating systems only deal with the symmetric host processors and uniform architectures leaving the management of co-processors to their device drivers.

In this chapter we present a survey of available heterogeneous hardware and software systems. We partition the discussion into Intel's software environment for the Xeon Phi (Section 2.1), an attempt to classify heterogeneous systems available (Section 2.2) and finally a Barrelfish related section (Section 2.3).

### 2.1 Intel Manycore Platform Software Stack

With the release of the Xeon Phi co-processors, Intel provided a software environment to support code offloading to the Xeon Phi in various modes such as Intel's MPI [18] architecture, native or offloaded execution [20]. Intel's Manycore Platform Software Stack (MPSS, [17]) supports Microsoft Windows [27] and Linux [63] hosts and includes a Linux-based co-processor operating system. We will go into more detail in Chapter 4 and Section 6.2.

The compute-model of Intel's MPSS treats each Xeon Phi in the machine as its own independent execution environment. From an operating system's perspective, the resulting design resembles a small cluster of independent networked machines rather than a single system. Communication between the nodes is made possible by a socket-like abstraction called Symmetric Communications InterFace (SCIF, [21]).

Even though the machine contains processors of different architectures, the operating systems do not have to deal with the heterogeneity. Similar to a networked cluster consisting of x86\_64 and ARM machines for instance, there is no management of multiple architectures by a single operating system. The Xeon Phi co-processor is treated as an ordinary PCI Express device.

### 2.2 Heterogeneous Systems

All of today's computers can be seen as heterogeneous. The degree of heterogeneity and how it appears highly depends on the system architecture and its intended use. The various designs can be classified into three models which can be combined.

### 2.2.1 Heterogeneous Networked Environments

Today's machines look like distributed systems [10]. However, a system is not limited to a single machine but can also be a cluster of networked nodes. Whereas a single machine is based on one architecture, the network has to deal with nodes of different types running a variety of operating systems and software. The resulting cluster is inherently heterogeneous. Several approaches to unify and manage networked resources have been investigated. The DAC Networked OS [31] provides resource sharing for a distributed co-operation between applications. 2K [47] deals with resource management in non-uniform, dynamic networks. However, networked environments do not deal with heterogeneity within a single machine.

### 2.2.2 The CPU plus Accelerator Model

This model is based on one or more main CPUs complemented with additional, specialized accelerators. One of the use cases for this model is to offload specific tasks to a hardware accelerator instead of doing the same computation with the general purpose CPU. This includes audio and video decoding using a DSP, cryptography applications or 3D imaging applications such as video games. Software frameworks like OpenGL [3] for instance provide the necessary abstractions. Accelerators are highly specialized hence not suitable for general purpose computing, especially as their output goes to one of the connectors. They are programmed by their respective device drivers.

Generalizing the accelerator model leads to a system consisting of a main CPU with programmable accelerators such FPGAs or core fusion [44] techniques. The resulting system is able to adapt to changing workloads. As the hardware features offered by the accelerator change depending on the programming, the hardware abstraction layer needs to be adapted as well. Nollet et al. [58] developed an operating system for reconfigurable SoC (OS4RS) based on a Linux real-time kernel. They are using a two level scheduling system where the top level manages task to processor assignment and per core lower level schedulers run the actual assigned task. Switching tasks between different core types can only be done at specific points during its execution.

### 2.2.3 The System-on-a-Chip Model

In today's mobile appliances, such as smartphones or tablets, the used CPUs are part of the so-called system-on-a-chip (SoC) architecture. One of the limiting factors for mobile applications is battery life and hence maximizing performance while minimizing the energy consumption are one of the driving factors. Similar

to the previous model, SoCs like the OMAP44xx [41] include specialized chips to do certain low-level tasks (energy) efficiently. As an illustrative example, one may consider playing an audio file with a dedicated audio DSP enabling the main CPU to go into a power save state.

Another aspect in the SoC scenario is to provide multiple cores with different performance characteristics while being based on the same architecture. Technologies such as ARM's big-little [50] are used to reduce the energy consumption of a chip. This setup can be viewed as pseudo heterogeneity where the architecture does not differ, but the compute-power and energy efficiency of the cores does. From an operating system's view switching between the different core types is like an extended change of the current C-state of the processor. The OS itself does not need to be heterogeneous. Replacing some bigger cores in a package with smaller ones can even be beneficial for certain workloads as shown by Kumar et al. [49] for Alpha processors and Li et al. [51] for Intel processors. The resulting chip is no longer symmetric. In both studies, they rely on a common instruction set architecture shared by all cores. This is comparable to some extent with the Xeon Phi as we will see in Chapter 4.

### 2.2.4 The Heterogeneous Model

The previous model can be seen as not fully heterogeneous: the secondary processors are either of the same architecture (*big-little*) or are too specific for general purpose computation (audio decoders).

Besides, the SoC model is also truly heterogeneous: the OMAP44xx [41], for instance, is based on two ARM Cortex A9 application processors which are accompanied by two ARM Cortex M3 multimedia processors. Both, the A9 and the M3 are general purpose CPUs but with different instruction set architectures (ISA) – in fact the ISA of the M3, Thumb 2, is also embedded in the ISA of the A9. Hence, an operating system utilizing both types needs to tackle the differences (see Section 2.3).

In the past, graphic processing units (GPUs) evolved into more general purpose compute platforms (GPGPUs). Streaming processors such as the nVidia Tesla (Section 4.2.3) are used for highly parallel workloads managed by software frameworks such as CUDA [60] or OpenCL [34]. Its general purpose design enables the use of GPGPUs in standard tasks such as sorting [32] or even networking [46].

In contrast to CPUs, the compute-model of GPGPUs is different and more challenging. Finding appropriate OS abstractions for GPGPUs is hard: Rossbach et al. [71] discovered the lack of proper OS abstractions for GPGPU resources such as fairness and isolation. They present *PTasks*, a parallel task API that simplifies the use of GPGPUs by abstractions to hide the orchestration as in CUDA [60]. With *PTasks*, the execution needs to be representable as a directed acyclic graph to match the streaming design of GPGPUs. Therefore, representing loops and conditionals is challenging and inefficient due to the warp scheduling of GPUs.

The question "What is Heterogeneous System Architecture (HSA)?" has also

been asked by AMD [4]. They discovered that main CPUs and accelerators/G-PUs have driven apart. Their aim is to come up with a re-design of the system architecture to feature a more integrated platform. They classified different processors into latency compute units (CPUs) and throughput compute units (GPGPUs) [2, 55]. In the current design of a system, data has to be made available for the co-processor which involves copying. They claim that tighter integration of CPU and GPGPU reduces communication latency and lowers the programming barrier. This trend can be observed today: Intel integrated its graphics processors into the CPU. The proposed HSA framework unifies the address space of CPU and GPU and enables data access from anywhere. However, as we show in Chapter 5 just being able to access data from anywhere does not necessarily result in a fast system: smart buffer placement strategies which reflect localities are of great importance.

Similar to *PTasks* and AMD's HSA the latest OpenMP Standard [62] enables executing certain code blocks on a specific target device. In heterogeneous systems the code segment can be executed on a device which supports certain hardware features such as extra wide vector units. However, the support for these pragmas is not fully available: "omp target constructs will always run on the host", as stated by GCC [39].

Wang et al. developed EXOCHI [79] which supports work distribution among CPU and integrated graphic accelerators by extending the OpenMP pragmas to support heterogeneous multi-threading. The modified OpenMP library produces architecture specific code for the host CPU as well as the GPU in one binary. Wang et al. used the integrated graphics accelerator of the Intel CPUs for offloading the computation.

Nightingale et al. developed Helios [57] which supports heterogeneous systems by providing an independent interface to applications. The programming model of Helios uses an intermediate compilation step: similar to Java byte code, Helios programs are first translated into an intermediate language and then compiled to the target architectures present on the system upon installation. This eliminates the burden of providing different versions of the same executable from the programmer. Further, Helios distinguishes between coordinator and satellite kernels. As the underlying architectures of satellite kernels may differ, Helios does not support a process to span multiple satellite kernels.

With Popcorn, Barbalace et al. [5] tried to bring support for heterogeneous architectures to the Linux operating system. They added another abstraction layer on top of multiple Linux kernels which provide a unified view of the system (Single System Image, SSI). They use messages between the Linux kernels to maintain the global system state in the SSI. In contrast to virtual machines, their kernels form a peer-to-peer rather than a client/server relationship.

### 2.3 Barrelfish

With its multikernel architecture (see Chapter 3), Barrelfish naturally supports a heterogeneous system architecture – as long as the processor is capable of

booting an OS node. Barrelfish tackles different types of dissimilarities such as non-uniformity, core diversity and system diversity [74] based on system knowledge [73]. So far, two approaches have been done in the context of heterogeneous systems.

As we will see in Chapter 4, Intel's Single Chip Cloud Computer (SCC) is one of the precursors of the Xeon Phi. In [53] a Barrelfish port was made supporting a heterogeneous architecture consisting on a host ( $x86\_64$ ) and the SCC ( $x86\_32$ ) running at the same time. The sophisticated design of the SCC required the handling of corner cases which are no-longer needed with the Xeon Phi. Further, the architecture used on the Xeon Phi matches the host architecture close enough that some problems such as different data type sizes do not exist. Barrelfish has dropped the support of the SCC [48].

Recall the two different types of cores on the OMAP44xx SoC [41]. An approach to get Barrelfish run on both cores has been undertaken in [30]. However, the implementation is not fully finished and the Barrelfish kernels running the M3 cores are not aware of the A9 cores in the system. This results in essentially two systems running concurrently on the same SoC.

To have Barrelfish make use of GPGPUs as an OS node would require to have a kernel running on the GPGPU. With the different compute model and streaming processor design this is not achievable as also discovered in [71].

Baumann et al. [9] have ported Barrelifsh to the prototype of the Xeon Phi called Knights Ferry<sup>1</sup>. They came up with a software system, COSH, which provided bulk transport facilities in a heterogeneous system. As in the recent Barrelfish bulk-transport project [1, 11], Baumann et al. aimed to provide clear semantics of transfers and enforce access rights to buffers.

### 2.4 Concluding Remarks

In summary, in general heterogeneous systems are nothing new and, depending on the definition, have existed for a long time as the example of video accelerator showed. However, most of the available systems today are not truly heterogeneous: their operating system deals only with one architecture at a time or having device drivers control co-processors as is the case with Intel's MPSS or nVidia CUDA.

There is a clear trend towards more diverse and less coupled systems. At some point commodity operating systems will have to deal with this heterogeneous architectures as the main processors of computers evolve from symmetric multiprocessors into asymmetric designs which might not even share a common instruction set architecture.

<sup>&</sup>lt;sup>1</sup>Due to the non-disclosure agreement the code is not available.

### Chapter 3

### Barrelfish in a Nutshell

In this chapter we will have a brief look at Barrelfish [68]: a research operating system developed at ETH Zurich with assistance from Microsoft Research [28]. The purpose of this Chapter is to set the foundation of the upcoming chapters by describing the most important building blocks and tools of Barrelfish. Readers that are already familiar with Barrelfish may skip this chapter. Starting with a general architectural overview (Section 3.1) and highlighting selected application domains (Section 3.3) we will have a look at resource management using capabilities (Section 3.2) and inter-domain communication using Flounder messages (Section 3.4). The remainder of this Chapter will talk about the domain specific languages for hardware access (Mackerel, Section 3.5) and for the build system (Hake, Section 3.6).

### 3.1 Architectural Overview

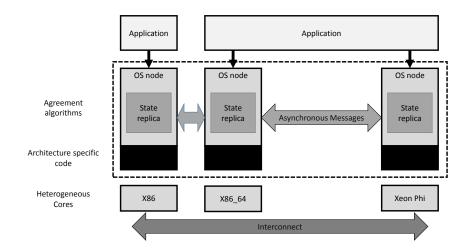

In contrast to the most common operating systems available, such as Linux [63] or Microsoft Windows [27] which are based on a monolithic or hybrid kernel, Barrelfish is based on a new kernel type called the multikernel [8]. An architecture scheme adapted to the Xeon Phi scenario can be seen in Figure 3.1.

Barrelfish tries to avoid sharing of state among cores, in other words, there are no global data structures. Each OS node has a local state replica which is kept up-to-date using message passing among the nodes. This enables lock-free, local access to system state. Barrelfish treats the machine as a distributed system [10]: Well-known agreement algorithms used in distributed systems ensure integrity of the state. As stated in [8], the fundamental model of a multikernel can be defined as:

- 1. All inter-core communication explicit.

- 2. Make OS structure hardware-neutral.

- 3. View state as replicated instead of shared.

Figure 3.1: Barrelfish Architecture

### 3.1.1 CPU Driver

In Barrelfish the kernel is referred to as the *CPU driver*. It abstracts architecture specific hardware details and executes in privilege mode. The tasks of the CPU driver involve context switching, memory isolation, fast local message passing and capability management, to name a few.

The CPU driver exports an architecture independent set of services and mediates access to the local hardware features such as the memory management unit or the local APIC. Interrupts are forwarded to the user-space driver domains in form of a message.

### 3.2 Capabilities

Resource management is a key concern of every operating system. In Barrelfish resources are managed using capabilities. Each capability has a certain type and may refer to a region of memory, a communication endpoint or an operation (capability invocation). Each domain has its own capability tree (CSPACE) which stores all the capabilities the domain obtained throughout its runtime. As capabilities are critical, only the kernel can access the CSPACE and create or modify capabilities. The domains refer to a specific capability with a reference to it – the address of the capability in the CSPACE.

If a domain wants to execute a privileged operation, it needs to pass the capability reference. The reference is looked up in the CSPACE and its containing capability validated. For instance, mapping memory requires presenting a frame capability during invocation. Domains can grant access to their resources by passing one of their capabilities to another domain. This can be viewed as a copy operation of an entry in the capability tree to another CSPACE.

In addition to copy there are several other operations that can be invoked on a capability depending on the type. A frame capability for instance can be split into smaller frames or reduced to a read-only mappable frame, to name a few. A complete description of a capability system in a multikernel environment was discussed in [56]. The current implementation state of the capability system can be obtained in the technical note [76].

### 3.3 Major Domains

In Barrelfish applications and processes are called *domains*. As already explained in the previous sections, the kernel of Barrelfish provides only the necessary set of services which need to be run with privileges. This design choice pushes many of the traditional kernel services to user-space domains. In this section we will have a look at a selection of Barrelfish's core domains.

### 3.3.1 Kernel Monitor

The design of Barrelfish tries to move as much as possible into user-space domains: only when necessary the CPU driver executes certain supervisor tasks. However, some operations are considered to be privileged with respect to the system state but do not need to be executed in supervisor mode. An example of this would be handling the capability transfer between domains. This tasks are handled by the Monitor which is trusted by the CPU driver. Some kernel services can only be invoked by presenting the kernel capability which only Monitor has. Another task of the Monitor is to exchange messages with the other Monitors in the system to update the OS state.

### 3.3.2 System Knowledge Base (SKB)

The idea behind the System Knowledge Base (SKB) is to store facts about the system such as which services are running, the number of on-line cores or the discovered hardware devices. Facts can be specified using a declarative language approach [73]: either statically or upon events during boot such as hardware discovery for instance. Providing a service interface, domains can query the SKB to obtain information about the system. A constraint solver is used to answer complex questions such as "What is the optimal PCI configuration given the available devices?"

Another part of the SKB is Octopus [80] which tracks events happening in the system. Domains can publish events or subscribe to them. Octopus can also be used as a key-value store for exported services (name-service functionality) or barriers for thread/process synchronization using message passing.

### 3.3.3 Memory Service

As explained above, every physical resource is represented as a capability and so are frames of memory. The design of Barrelfish moves the management of physical memory into the user-space domain memserv. During boot up, memserv

is spawned by the init domain and initialized with the capabilities of all the unused frames. If a domain needs memory, it sends a request to the service and obtains a RAM capability which best suits the size and address constraints of the request. It retypes it into a frame or page table capability depending on the use.

#### 3.3.4 Device Drivers

In contrast to other operating systems such as Linux where device drivers are part of the kernel, Barrelfish has its device drivers running in user-space. Each device driver is given access to its registers using a capability representing the MMIO range of the device. The capability is then mapped directly into the driver's virtual address space. This enables the driver to access the device without kernel involvement. Device drivers export a specified service interface to handle requests from other domains over message passing. Interrupts are transformed into messages by the kernel and handled by the user level driver.

### 3.4 Message Passing

Barrelfish's architecture demands efficient user-level message passing for communication between the domains especially replicating OS state. In Barrelfish this is abstracted using a tool called Flounder. The messaging interfaces are described in a domain specific language (DSL). The DSL compiler generates message passing stubs which are used by the domains to send and receive messages. Flounder supports multiple messaging backends. The following two subsections briefly describe the export and bind processes. For a more detailed description of the DSL and the operations refer to the technical note about inter-dispatcher communication [7].

### 3.4.1 Exporting a Service

A flounder channel is based on two endpoints: a service (exporting) side and a client (binding) side. Domains acting as servers initialize the service side of the interface by *exporting* it. Each exported Flounder interface can be identified by an IREF which is assigned by the Monitor during the export process. The kernel Monitor will store the IREF-to-endpoint mapping. To make the IREF known to other domains it can be registered with the name-service.

### 3.4.2 Binding to a Service

To use a service, a domain needs to *bind* to the exported IREF. The IREF can be looked up using the name service or passed by other means directly with program arguments for instance. Monitors keep a IREF to endpoint association which is used to bootstrap the communication channel. With the help of the Monitor a shared frame is initialized between the domains (In case of the user-level message passing backend).

### 3.5 Hardware Register Access

Device drivers need to be able to access the hardware registers of the device. Recall in Barrelfish resources are represented using capabilities and since memory mapped hardware registers are resources, a capability is needed to access them. Once the registers are made accessible to the driver domain, writing and reading specific bits is tedious and error prone. Barrelfish uses another domain specific language called Mackerel [67] to simplify reading and writing hardware registers or describing the layout of in-memory descriptors. The DSL specification is compiled into a C header file which provides the necessary functions to access the registers.

### 3.6 Hake: Barrelfish's Build System

With a broad diversity of supported architectures, it is necessary to have a suitable build system which can handle the different architectures, dependencies and domain configurations well. Barrelfish uses a tool called Hake [70] to work out which domains to build and how they are compiled.

To build Barrelfish, Hake is initialized in the build directory and configured with a one or more specified architectures. During the initialization, Hake will walk through the source tree and find all the Hakefiles and evaluates them.

#### 3.6.1 Hakefiles

For the CPU driver and each domain, library or tool there is a Hakefile specifying how to build the target. Based on the Hakefiles the dependencies are generated and in the end a *Makefile* is generated.

The following code snipped shows an example Hakefile with the added dependencies of libraries, Flounder interfaces as well as Mackerel device specifications.

Listing 3.1: Sample Hakefile

### Chapter 4

## The Intel Xeon Phi Co-Processor

As with any new hardware, one generally wants to know its features, differences and similarities to other well-known products or architectures, especially x86\_64 in our case. In this chapter we will have a look at the first generation Intel Xeon Phi co-processor [23] (code-name Knights Corner, KNC). After providing historic information, we start this chapter with an overview of a possible system configuration (Section 4.1) and a section about the hardware features of the Xeon Phi (Section 4.2). Following, a section about the new k1om architecture with a brief comparison to x86\_64 (Section 4.4). The last part will investigate the boot process (Section 4.5) and its implications for the Barrelfish operating system.

| Code Name       | Year | Notes                                     |

|-----------------|------|-------------------------------------------|

| TRP             | 2006 | Tera-Scale Research processor             |

| Larrabee        | 2007 | Prototype (GPGPU)                         |

| SCC             | 2009 | Prototype to promote Many Core Research   |

| Knights Ferry   | 2010 | Prototype of the Xeon Phi (MIC Prototype) |

| Knights Corner  | 2013 | Xeon Phi Generation 1                     |

| Knights Landing | 2015 | Xeon Phi Generation 2                     |

Table 4.1: Xeon Phi Historic Overview

History To set the historic context of the Xeon Phi, we crawl back in time and present the Intel Labs projects that lead to the current Xeon Phi product line. Table 4.1 summarizes the evolution of the Intel Many Integrated Core Architecture (MIC, [26]) micro architecture. In 2006 Intel demonstrated an 80 core Tera-Scale Research Processor (TRP) [38] which had limited features but served as a learning tool for the upcoming 48 core Single Chip Cloud Computer (SCC) [14]. While the TRP had only simple cores, the SCC came with a network of 48 fully functional Pentium based cores. With the Larrabee project [75], a general purpose graphics processor (GPGPU), Intel wanted to bring a new

graphics chip design based on many in-order x86 cores. However, the Larrabee project was discontinued in 2010.

In 2010 Intel presented the Knights Ferry, the first prototype of the MIC architecture; in other words the prototype of the Xeon Phi co-processors, targeting high performance computing applications. The Knights Ferry can be viewed as a derivative of the previous many core projects Larrabee, TRP and SCC [15]. Evolving from the Knights Ferry, the Knights Corner features more cores, more memory and a peak performance of one teraFLOPS. The Knights Corner was released as the first generation of the new Xeon Phi brand and was made available to customers [23] in 2013. In 2014, Intel announced the second generation of the Xeon Phi, code-name Knights Landing, to be released in 2015 [22].

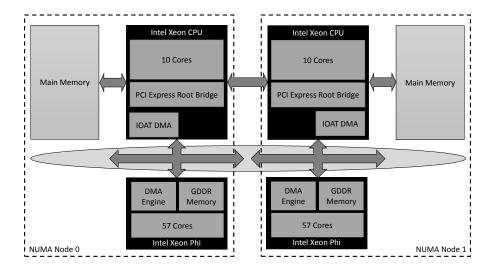

### 4.1 System Overview

Before we start with investigating the features of the Xeon Phi co-processor, we present a summary of the system we use throughout our evaluation. Table 4.2 below summarizes the most important numbers concerning the later evaluation of the proposed system. For a detailed description of the hardware refer to the respective hardware manufacturer information pages such as Intel ARK [25]. To illustrate the NUMA setup of the machine a schematic layout of the system can be seen on Figure 4.1 on page 24. Note that the I/O Acceleration Technology (I/OAT) DMA controllers are part of the CPU and described in the processor data sheet [43, Chapter 8.4] rather than residing on the chip-set, despite the fact that they show up as a PCI Express device.

| Feature      | Value                               |

|--------------|-------------------------------------|

| CPU          | 2x Intel(R) Xeon(R) CPU E5-2670 v2  |

|              | 10 cores, Hyper-threading, 2.50 GHz |

| Architecture | Ivy Bridge                          |

| Memory       | 256 GB DDR3-1600                    |

| NUMA         | 2 NUMA Nodes                        |

| Xeon Phi     | 2x Xeon Phi 3210A                   |

| Network      | Intel I350 Gigabit Ethernet         |

| DMA          | I/OAT Crystal Beach Version 3.0     |

Table 4.2: System Description

### 4.2 Xeon Phi Co-Processor

This section describes the hardware features of the Xeon Phi and compares them to other well-known architectures such as Intel Ivy Bridge or nVidia Tesla. The reader must be aware of the different models of the Xeon Phi which are currently available each of which vary in certain figures of their specification while others are consistent among the models. We restrict ourselves to the presentation of the Xeon Phi model 3210A which will be used in the later evaluation. For a

Figure 4.1: System Overview with Xeon Phi

complete of the available models comparison the reader may refer to the Xeon Phi data sheet [19] or Intel Ark [25].

### 4.2.1 Hardware Specification

The Xeon Phi is not an ordinary processor plugged into the mainboard socket but a co-processor which is connected over the PCI Express Bus [65]. Hence, it appears as a PCI device to the host operating system. Table 4.3 on page 25 shows a comparison of the Xeon Phi with the Xeon E5 v2 series and the current nVidia Tesla architecture. The values were extracted from their respective data sheets [42, 19, 59]. The following two subsections highlight a selection of differences between the Xeon Phi compared with the Xeon E5 v2 and nVidia Tesla respectively.

### 4.2.2 In Comparison with the Xeon E5 v2

Despite the fact that both architectures are based on variations of x86, there are several striking differences between the Xeon E5 v2 and the Xeon Phi: The Xeon E5 v2 is a multi-core CPU with 10 out-of-order cores and 2 hardware threads each whereas the Xeon Phi is a many-core CPU with 57 in-order cores and 4 hardware threads each. On the one hand, the Xeon E5 v2 uses a 3-level caching structure with a large L3 cache, on the other hand the Xeon Phi has a two level caching structure. Additional information about the Xeon Phi caches can be found in Section A.1. The next difference we want to emphasize is the type of supported main memory: the Xeon E5 v2 uses the DDR3 standard with various speeds ranging from DDR3-800 up to DDR3-1866, whereas the Xeon Phi has GDDR5 type memory built onto the co-processor card. Both types of memory are designed for special purposes and have different performance characteristics. As a rule of thumb, GDDR is designed to target high throughput streaming applications while DDR is adapted towards random access patterns

|                    | Xeon E5                           | Xeon Phi               | nVidia Tesla        |

|--------------------|-----------------------------------|------------------------|---------------------|

| Feature            | 2670  v2                          | 3210A                  | Kepler K40          |

| Cores              | 10                                | 57                     | 15                  |

| Type               | Out-of-Order                      | In-Order               | Streaming           |

| Threads            | 20                                | 228                    | 2880                |

| Clock Speed        | $2.5~\mathrm{GHz}$                | $1.1~\mathrm{Ghz}$     | $0.88~\mathrm{GHz}$ |

| L1 Cache           | 32kB + 32kB                       | 32kB + 32kB            | 16-48kB             |

| L2 Cache           | $256 \text{kb} \ (2.5 \text{MB})$ | 512kB (28.5MB)         | 1.5MB               |

| L3 Cache           | 25MB                              | -                      | -                   |

| Coherence Protocol | MOESI                             | MESI + GLOS            | n/a                 |

| Extensions         | Intel AVX                         | IMCI                   | CUDA                |

| Memory (Max)       | 768GB DDR3                        | 6GB GDDR $5$           | 12GB GDDR5          |

| Memory Channels    | 4                                 | 12                     | n/a                 |

| Memory Bandwidth   | $59.7 \; \mathrm{GB/s}$           | $240 \; \mathrm{GB/s}$ | $288 \mathrm{GB/s}$ |

| Physical Address   | 46 Bit                            | $40  \mathrm{Bit}$     | n/a                 |

| PCI Express Rev    | 3.0                               | 2.0                    | 3.0                 |

| DMA Channels       | 8x (IOAT)                         | 8x                     | 2x                  |

| Peak Performance   | 0.46  Tflops                      | 1.00  Tflops           | 1.43 Tflops         |

Table 4.3: Xeon Phi Hardware Specification

and low latency. The effects on memory access latency and throughput will be investigated in Chapter 5.

Last, one may notice the PCI Express revision on the comparison. As the Xeon E5 acts as the root complex of the PCI Bus, the Xeon Phi will be a PCI client in the system. It is possible to have up to 8 Xeon Phi co-processor in a single host system.

### 4.2.3 Comparison to General Purpose GPUs

General purpose GPUs (GPGPUs) are comparable to the Xeon Phi as both are co-processors with a huge number of cores and thus providing massive parallelism for high performance computing. Despite the closeness in terms of target applications, their differences are fundamental: The Xeon Phi offers x86 based cores whereas GPGPUs such as nVidia Tesla are so-called streaming processors. This is reflected in their programming model. In order to program nVidia Tesla co-processors the CUDA ecosystem [60, 61] has to be used which provides a framework to offload computations onto the co-processor. In contrast to the mainly host driven CUDA, the Xeon Phi is capable of running an operating system such as Linux or Barrelfish providing autonomous services. Even though there would be many more things to discuss, a more in depth comparison between the Tesla and the Xeon Phi co-processors is out of scope for this thesis.

### 4.3 Physical Address Space Layout

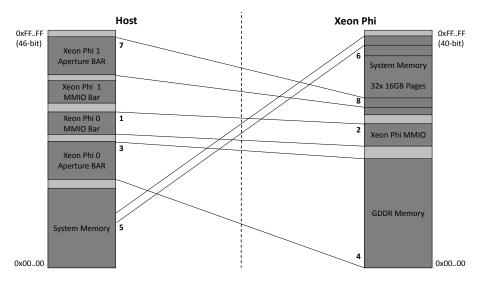

In commodity systems, the physical address space layout is based on the assumption that there is an injective mapping between physical address and a byte in main memory. Looking at a system with one or more Xeon Phi co-processors, – note that this is not generalizable for all co-processors – one recognizes that this uniqueness assumption no longer holds. A scheme of the resulting address space layout can be seen on Figure 4.2 below. The following subsections explain the layout and its implications towards the understanding of physical memory.

Figure 4.2: Address Space Layout of a System with Xeon Phi Co-Processors

#### 4.3.1 Host Side View

At a first glance, there is not much different in the physical address range as seen from the host side: the Xeon Phi will appear as a normal PCI Express device with two memory regions which are of interest for us (numbers in parentheses refer to Figure 4.2):

- MMIO Space The memory mapped IO range (1) is 64 kB in size and consists of the device registers (2) to control the co-processor such as initiate the boot sequence or programming the DMA channels. It is important to note, that the access to the MMIO registers from the host side is limited.

- Aperture Space This memory region maps the Xeon Phi's GDDR memory (4) into the host physical address space (3). The size of this region varies between the models from 8GB to 16GB<sup>1</sup>.

Two additional regions, the IO range and EXPROM aperture, need to be activated separately and are not of interest for our use case.

<sup>&</sup>lt;sup>1</sup>The PCI aperture is rounded to the next power of two, the driver programmer has to be aware of the effective size depending on the model as the aperture may suggest a bigger size.

#### 4.3.2 Xeon Phi Side View

On the Xeon Phi there are several memory regions available some of which are also accessible from the host.

- GDDR Memory This memory region (4) is the main memory of the Xeon Phi co-processor. An operating system running on the card will treat this memory region as normal RAM. The GDDR Memory region is also mapped as aperture (3) on the host.

- MMIO The memory mapped IO registers (2) are located in the so-called SBOX (PCI Express client logic) of the Xeon Phi. While access to the MMIO space is limited from the host, an operating system running on the co-processor can access all 666 registers.

- System Memory The top half of the physical address range on the Xeon Phi is called system memory range (6). The size of this region is 512GB. The system memory range is further divided into 32 pages of 16 GB each.

The physical address range of the Xeon Phi is only 40 bits in contrast to the 46 bits of the host (Sandy Bridge micro architecture)

### System Memory Page Table

Each of the 32 system memory pages can be configured by writing the address into one of the consecutive system memory page table (SMPT) registers in the MMIO space. Each page can be programmed to map any 16 GB of host physical memory into the address space of the Xeon Phi. The memory block has to be 16GB aligned and must be exactly 16GB in size. Considering the Xeon Phi as a guest, one can draw analogies between configuring the SMPT and setting up of shadow page tables or extended page tables in a virtualized environment. Following we discuss the implications of the system memory range towards the understanding of physical address spaces.

### 4.3.3 Multiple Physical Address Spaces

In a system without co-processors there is a single physical address space to be managed by the operating system. Recall the assumptions made by the operating system about the uniqueness of references to an addressable byte in the physical address space. In the following we present the fundamental changes and their implications when dealing with a heterogeneous, Xeon Phi enhanced system.

### Ambivalence of Physical Addresses

The uniqueness assumption that each byte in memory has exactly one physical address does not hold anymore. Consider the following example:

Let's assume we have a byte at address A in the main memory of the host. Viewed from the host side this address A is unique. Switching side, viewed

from the co-processor this byte in memory is now at address B resulting in two different addresses for the very same byte. To stress out the issue even more, the SMPT can be programmed in such a way that byte A now also appears at addresses C and D or it may not be existing at all.

In addition, let's assume there is an address G in every address space present in the system. Obviously, this address is valid in all address spaces but refers to another byte in memory or even a something different like a hardware register. Therefore, we have the same name pointing to different things.

With up to 8 Xeon Phi co-processors supported in a single system, there is the possibility that an address A in the host physical address space is mirrored in any of the co-processors address ranges. One may go even further and map the aperture spaces of the Xeon Phi in the SMPT. That way it is possible to have to distinct co-processor local addresses point to the same local address in GDDR memory.

#### Non-consistent Physical Addresses

Like the extended page tables in virtualized environments, the SMPT may be configured at any point of time. Hence, the physical addresses in the system memory range of the Xeon Phi behave more like virtual addresses rather than real physical addresses. The result of this is a broken assumption that a physical address space always refers to the same byte in memory – we assume that the PCI devices BARs are not altered once programmed.

#### **Implications**

Based on the above stated observations we claim that a single machine no longer has a single physical address space. We rather have a multiple address space scenario which are interleaved: system memory and co-processors GDDR can be accessible from both sides. A multiple address space scenario raises new questions and has several implications:

- What is a physical address space? This question is even more important when we consider methods to access remote memory directly such as RDMA, PCI aperture or system memory ranges.

- How are bytes in memory referenced? The design of Barrelfish allows that the system to span a heterogeneous setup such as ours with a host and Xeon Phi co-processors. Hence, it is possible to pass capabilities around which implies that we must make sure that address A (a byte in memory on the host) is translated into an address B on the Xeon Phi referring to the same byte in memory.

- How are physical address spaces identified? Having multiple physical address spaces accessible in a system means that there might be a physical address A which is valid in all address spaces, but refers to different regions in memory. Consequently, we need a way to uniquely refer to a specific address space. This is even more important with technologies such as RDMA where it is possible to access memory of a remote system.

- Trust Issues: The fact that the co-processor OS can access system memory may lead to unintended or malicious access of main memory<sup>2</sup>. Even with appropriate programming of the SMPT, the coarse granularity of the pages is not suitable for access control. In that case, the use of an IOMMU is highly encouraged.

- Malicious co-processor OS: Even though the host OS loads the coprocessor OS onto the card, once it is running it is out of host's control. The host must trust the co-processor OS not to mess with host memory and vice versa. This can be reduced to a similar problem in virtual environments: the hypervisor needs to be trusted.

These implications are a research topic on their own and would be out of scope for this thesis. Some of the points stated above had to be solved during the development of the system and are described in Chapter 6.

### 4.3.4 Accessing Resources of another Processor

So far we have explained how the host can access the GDDR of the co-processor. However, it may be the case that multiple Xeon Phi co-processors are present in the system and they want to communicate with each other without host involvement. Therefore, it must be possible to access the GDDR of another Xeon Phi co-processor directly. This can be done by programming one entry of the SMTP with the host physical address of the aperture space of the other Xeon Phi.

This clearly adds the 16GB alignment constraints for the PCI aperture space when programming the PCI device BARs. The problem boils down to the Xeon Phi host side driver knowing where the other Xeon Phi's apertures are mapped and which slot to program. A possible solution to this will be presented in Chapter 6.

### 4.4 The K1OM Architecture

Intel introduced a new architecture called k10m which is an adaption of the well-known x86\_64 architecture. There are several differences between standard x86 and the new k10m architecture which we will elaborate in this Section. So far, every new generation of processors was backwards compatible. This is not the case with the Xeon Phi. Most of the changes are considered to be a limitation of features on which out-of-the-box operating systems may rely. Hence, system software needs to be adapted to the new environment and the new instruction set architecture. The following paragraphs describe the major differences and its implications to the operating system intended to run on the Xeon Phi. For a complete list of limitations refer to the Xeon Phi Systems Software Developer Manual [20] or the Xeon Phi Instruction Set Architecture [16].

<sup>&</sup>lt;sup>2</sup>It is generally assumed that the host trusts the co-processor not to mess with the host system. This assumption is justified by the fact that everything that is loaded on the co-processor somehow has to go through the host.

**Compatibility Mode** In general, processors supporting long mode have a compatibility sub mode which can handle 32-bit applications without recompilation. Even though the Xeon Phi is 64-bit, the compatibility sub mode is not available.

SIMD and Vector Instructions Intel equipped the Xeon Phi with extra 512-bit wide vector registers while truncating the support of the smaller MMX and SSE instructions (xmm and ymm registers). Only 512-bit registers (zmm) are supported, instructions using the smaller vector units trigger a unsupported instruction fault.

**Local APIC** With the increased number of cores and hardware threads, the APIC ID fields of standard x86\_64 are too small to reference all threads. Therefore, the APIC on the Xeon Phi does have extended APIC ID representations. Operating system must take the changed bit representation into consideration when booting new cores or issuing interrupts. Note that interrupts can not only target a local core but also a core on the host or another Xeon Phi card in the system.

**Timer Hardware** The commonly found timer hardware such as the programmable interrupt timer or the advanced configuration and power interface (ACPI) are not present on the Xeon Phi. This implies that the operating system must use the local APIC for timer interrupts and scheduling.

Global Page Tables The Xeon Phi does not support the global bit in the page directory entries or the page table entries. Attempts to enable it by writing the enable bit into CR4, will trigger a global protection fault.

Memory Prefetching To optimize certain memory operations in the standard C library, memory prefetch instructions are used. Normal prefetch operations are not available, but the Xeon Phi Instruction Set Architecture manual describes the new instructions that can be used.

Memory Ordering As the memory model of the Xeon Phi is stricter than the x86\_64 model, reads and writes to the memory appear in program order. This stricter model eliminated the need for memory ordering instructions such as MFENCE or SFENCE.

I/O Devices Similar to system on a chip designs (SoC) the Xeon Phi does not have a PCH south-bridge. Therefore, lots of devices that normally reside on the PCI bus are not present on the Xeon Phi. Without I/O devices present, the in and out instructions are not supported.

**Serial Port** Even though the Xeon Phi has a serial port, it is not directly usable. The port is located at the far end of the I2C bus and it is tedious to access. In addition one needs to connect additional hardware to the card in order to get the output. Thus, serial output needs to be handled otherwise.

### 4.5 Booting the Xeon Phi

The boot procedure of the Xeon Phi consists of several stages and boot modes. This section will briefly discuss the different boot modes (Section 4.5.3), supported operating systems (Section 4.5.1) and the booting process itself (Section 4.5.2). For a complete and more detailed boot process description one may refer to the Xeon Phi System Software Developers Guide [20].

### 4.5.1 Operating Systems

The limitations and differences to the x86\_64 architecture (as explained in Section 4.4) implies that operating systems will most likely not work out of the box. In the Intel provided software stack, a modified Linux is already included. In any case, after the required modifications are incorporated into the code, the Xeon Phi is capable of booting any operating system referred to as third party OS.

### 4.5.2 Bootstrap

In contrast to a normal x86 system where s a BIOS handles the early boot stages, there is no BIOS on the Xeon Phi. The early boot tasks are handled by the so-called *bootstrap* which is executed on power-on and reset events. It consists of two different stages: fboot0 and fboot1.

#### Stage 0: fboot0