DISS. ETH NO. 26619

# **On Memory Addressing**

A thesis submitted to attain the degree of

Doctor of Sciences of ETH Zurich

(Dr. sc. ETH Zurich)

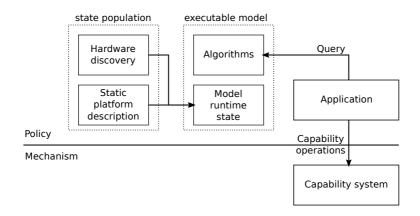

presented by

### **Reto** Achermann

Master of Science ETH in Computer Science, ETH Zurich

born on 04. June 1989

citizen of Ennetbürgen, Switzerland

accepted on the recommendation of

Prof. Dr. Timothy Roscoe (ETH Zurich), examinerProf. Dr. David Basin (ETH Zurich), co-examinerProf. Dr. Gernot Heiser (UNSW Sydney), co-examinerDr. David Cock (ETH Zurich), co-examiner

2020

On Memory Addressing. Copyright © 2020, Reto Achermann.

Permission to print for personal and academic use, as well as permission for electronic reproduction and dissemination in unaltered and complete form are granted. All other rights reserved.

DOI: 10.3929/ethz-b-000400029

Operating systems manage and configure a machine's physical resources such as memory and translation hardware. This task is mission critical: the operating system must always correctly configure memory address translations and unambiguously name the physical resources of a system. However, operating systems today use abstractions and assumptions which unfaithfully represent the actual topology of the hardware they are managing. This mismatch leads to bugs and security vulnerabilities in system software. This is a problem.

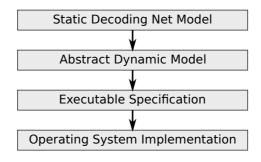

This dissertation presents a new abstraction model to faithfully represent the memory subsystem of a hardware platform as seen by software. The core abstraction of the new model is the address space, which defines the context for address decoding. An address space either translates addresses or terminates address resolution within its context. The *Decoding Net* formally specifies the semantics of address decoding behavior of address spaces in the Isabelle/HOL theorem prover. This provides a sound basis for reasoning about the current hardware configuration of a platform.

Address spaces are inherently dynamic in two ways: *i*) new devices are discovered, powered on or off, or hot-plugged introducing new address spaces in the system, and *ii*) a memory allocation request requires an update of the translation configuration of an address space. Changing the configuration of an address space is a privileged operation and requires a certain authority. This is expressed as an extension to the *Decoding Net* with a layer adding a notion of configurability and fine-grained authority following the principle of least-privilege.

Guided by an executable specification of the dynamic *Decoding Net* model, the implementation in *Barrelfish/MAS* is driven following the principle of least-privilege. The resulting implementation demonstrates that it is possible to implement the detailed address space model and least-privilege memory management in an operating system efficiently and with little overhead and matching performance to the Linux operating system.

Betriebssysteme verwalten und konfigurieren die physikalischen Ressourcen wie Hauptspeicher und Adressierungsübersetzungshardware einer Rechenmaschine. Dieser Arbeitsschritt ist missionskritisch: das Betriebssystem muss die Hardware stets korrekt konfigurieren wie auch die physikalischen Ressourcen des Systems eindeutig benennen können. Die Betriebssysteme von heute benutzen jedoch Abstraktionen und Annahmen welche gerade die eigentliche Topologie der verwalteten Hardware inakkurat repräsentieren. Diese Diskrepanz führt zu verschiedensten Defekten und Sicherheitslücken in System Software. Dies ist ein Problem.

Diese Dissertation präsentiert einen neues Abstraktionsmodell welches die Hardwarekonfiguration einer Rechenmaschine, wie sie von der Software gesehen wird, akkurat repräsentiert. Die Zentrale Abstraktion dieses neuen Modells ist der Adressraum, welcher einen Kontext für Adressdekodierung definiert. Ein Adressraum übersetzt oder schliesst die Adressauflösung für eine Adresse innerhalb seines Kontextes ab. Die Semantik der Adressauflösung und der Adressräume ist dann formalisiert im "*Decoding Net*", eine Spezifikation der Adressraumabstraktion in Isabelle/HOL. Dies bildet eine wohldefinierte Grundlage, um über die gegenwärtige Hardwarekonfiguration einer Plattform zu argumentieren.

Die Adressräume sind von Natur aus dynamisch in zwei Arten: *i*) das Auffinden, Anschliessen oder Entfernen von neuen Hardwarekomponenten verändert die Anzahl der Adressräume im System, und *ii*) die Konfiguration dieser Adressräume kann verändert werden. Diese privilegierte Aktion benötigt die entsprechenden Befugnisse. Das "*Decoding Net*" Modell wird erweitert mit einer Auffassung von Konfigurierbarkeit und detailgenauen Befugnissen im Sinne von Prinzip des minimalen Rechts.

Gelenkt von einer ausführbaren Spezifikation des dynamischen "Decoding Net" Modells wird die Implementierung in Barrelfish/MAS durchgeführt unter dem Prinzip des minimalen Rechts. Die resultierende Implementierung zeigt, dass es möglich ist das detaillierte Adressraummodell und eine Speicherverwaltung mit minimalen Rechten effizient in einem Betriebssystem zu realisieren.

I am exceptionally thankful to my many amazing and wonderful friends and colleagues, who contributed, in some way or another, to the research presented in this thesis.

To my adviser, Prof. Timothy "Mothy" Roscoe. Thank you for giving me the opportunity to do my masters and doctoral studies in the Systems Group. I am truly grateful for your openness, support, and the feedback and advice I have received from you during my time at ETH Zurich. It was a great pleasure to work with you.

To Dr. David Cock. I am exceptionally grateful for the opportunity to work with you. Thank you for your inputs to the formal modeling, constructive feedback, and Isabelle/HOL expertise, which enabled and propelled many aspects of the work presented in this thesis.

To Prof. Gernot Heiser. Thank you for agreeing to be on my committee, and your outstanding dedication in providing valuable feedback and insightful comments, which greatly improved my dissertation.

To Prof. David Basin. I appreciate that you have agreed to be on my committee, and your valuable and assuring feedback on the dissertation.

To my outstanding and truly exceptional collaborators at ETH Zurich, Hewlett-Packard Labs, VMware Research and elsewhere. I would like to express my greatest gratitude for giving me the opportunity to work and collaborate with you. Your dedication, comments and feedback during many meetings and interactions, and contributions to papers, reports and projects either directly or indirectly contributed to my dissertation: David Cock, Lukas Humbel, Roni Häcki, Simon Gerber, Jayneel Gandhi, Dejan Milojicic, Kornilios Kourtis, Stefan Kästle, Michael Giardino, Nora Hossle, Daniel Schwyn, Gerd Zellweger, Moritz Hoffmann, Ashish Panwar and Abhishek Bhattacharjee.

To my friends and colleagues at ETH Zurich. Roni, Pravin, Renato, Simon, Stefan, Frances, Michael, Claude, Moritz, Gerd, Daniel, David, Nora,

Anastasiia, Andrea, Lukas, Melissa, Michael, Monica, Raphael, Daniel and Barbara. Thank you for making my time in the Systems Group such a great experience. A special thank you to the amazing admins of the Systems Group: Simonetta, Nadia, and Jena.

Finally, I would like to thank my parents, Irene and Beppi, for their unconditional support.

Zurich, February 2020.

| 1 | Intr | oduction                                                                                                                                                              | 1                          |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1  | Motivation                                                                                                                                                            | 2                          |

|   | 1.2  | Problem Statement                                                                                                                                                     | 5                          |

|   | 1.3  | Structure of the Dissertation                                                                                                                                         | 7                          |

|   | 1.4  | Related publications                                                                                                                                                  | 9                          |

| 2 | Prol | blem Statement                                                                                                                                                        | 11                         |

|   | 2.1  | Motivation                                                                                                                                                            | 11                         |

|   | 2.2  | Survey of Memory Address Translation2.2.1Address Spaces and Address Definitions2.2.2Translation Schemes in Real Hardware2.2.3Proposed Translation Schemes2.2.4Summary | 12<br>13<br>18<br>35<br>43 |

|   | 2.3  | Current Physical Address Space Model                                                                                                                                  | 43                         |

|   | 2.4  | Problems with the Current Model                                                                                                                                       | 45<br>45<br>56             |

|   | 2.5  | Implications for Operating System Architectures2.5.1Operating System Design Implications2.5.2Virtualization as a Solution?2.5.3Operating System Design Challenges     | 58<br>59<br>60<br>61       |

|   | 2.6  | Conclusion                                                                                                                                                            | 63                         |

| 3 | Rela | ited Work                                                                                                                                                             | 65                         |

|   | 3.1  | System Topology Descriptions3.1.1Self-Describing Hardware and Firmware3.1.2Domain Specific Languages                                                                  | 66<br>66<br>67             |

|   |      | 3.1.3                                                                         | System Topologies Summary                                                                                                                                             | 69                                                 |

|---|------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 3.2  | Behavi<br>3.2.1<br>3.2.2<br>3.2.3                                             | ioral System Descriptions                                                                                                                                             | 69<br>69<br>71<br>72                               |

|   | 3.3  | Memor<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8 | ry Management in Operating Systems Monolithic Operating Systems                                                                                                       | 72<br>73<br>74<br>75<br>77<br>80<br>80<br>82<br>83 |

|   | 3.4  | Runtin<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                           | ne Systems and Programming LanguagesMemory Topology ModelsCache Topology ModelsCo-Processor OffloadingProgramming LanguagesRuntimes and Programming Languages Summary | 83<br>84<br>86<br>87<br>88<br>89                   |

|   | 3.5  | Summ                                                                          | ary                                                                                                                                                                   | 89                                                 |

| 4 | A Fo | ormal M                                                                       | lodel for Memory Addressing                                                                                                                                           | 91                                                 |

|   | 4.1  | Motiva                                                                        | ation                                                                                                                                                                 | 92                                                 |

|   | 4.2  | An Ac<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                     | curate Model for Memory Address TranslationFormulation as a Naming ProblemAddress Resolution and Memory AccessesSystem RepresentationDiscussion                       | 94<br>95<br>98<br>100<br>102                       |

|   | 4.3  | Model<br>4.3.1<br>4.3.2                                                       | Definition                                                                                                                                                            | 103<br>104<br>104                                  |

|   |                                                           | <ul><li>4.3.3 Decoding Net Definition</li></ul>                                                                                                                                                       | 106<br>108                                    |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   | 4.4                                                       | System Descriptions and Syntax                                                                                                                                                                        | 109<br>109<br>111                             |

|   | 4.5                                                       | Algorithms                                                                                                                                                                                            | 115<br>115<br>116<br>119                      |

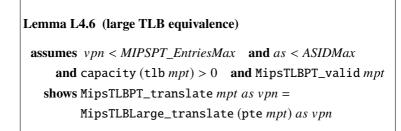

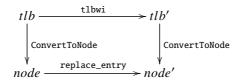

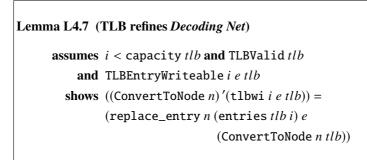

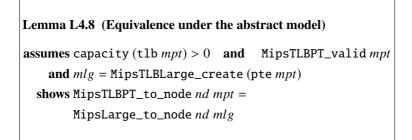

|   | 4.6                                                       | Modeling the MIPS R4600 TLB4.6.1The TLB Model4.6.2The Validity Invariant4.6.3Modeling TLB Translations4.6.4The TLB Refines a Decoding Net4.6.5Specification Bugs4.6.6Comparison to an ARMv7 TLB Model | 125<br>126<br>130<br>133<br>143<br>146<br>150 |

| 5 | 4.7<br>Dvm                                                | Conclusion                                                                                                                                                                                            | 150                                           |

| 3 |                                                           |                                                                                                                                                                                                       |                                               |

|   |                                                           | -                                                                                                                                                                                                     | 153                                           |

|   | 5.1                                                       | Motivation                                                                                                                                                                                            | 154                                           |

|   | 5.1<br>5.2                                                | Motivation                                                                                                                                                                                            | 154<br>157                                    |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Motivation       Bookkeeping and Access Control       Methodology                                                                                                                                     | 154<br>157<br>160                             |

|   | 5.1<br>5.2                                                | Motivation                                                                                                                                                                                            | 154<br>157                                    |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Motivation       Bookkeeping and Access Control       Methodology                                                                                                                                     | 154<br>157<br>160                             |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Motivation                                                                                                                                                                                            | 154<br>157<br>160<br>163                      |

| 6 | Ope  | rating System Support for Dynamic Decoding Nets                                                                                                                                                                                                                                | 179                                                         |  |  |  |  |  |  |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|--|

|   | 6.1  | General Implementation Considerations                                                                                                                                                                                                                                          | 180<br>180<br>181<br>182<br>184                             |  |  |  |  |  |  |  |

|   | 6.2  | Proposal of a Possible Implementation in a Monolithic<br>KernelKernel6.2.1Reference Monitor6.2.2Authority with Access Control Lists6.2.3Physical Resource Management6.2.4Explicit Address Spaces6.2.5Managing Address Translation6.2.6Address-Space Aware Cores6.2.7Conclusion | 185<br>185<br>187<br>189<br>191<br>192<br>193<br>194        |  |  |  |  |  |  |  |

|   | 6.3  | Implementation in Barrelfish/MAS6.3.1Reference Monitor6.3.2Background on Capabilities in Barrelfish6.3.3Physical Resource Management6.3.4Explicit Address Spaces6.3.5Managing Address Translation6.3.6Address-Space Aware Cores6.3.7Runtime Support6.3.8Compile Time Support   | 194<br>195<br>195<br>199<br>200<br>204<br>206<br>207<br>211 |  |  |  |  |  |  |  |

|   | 6.4  | Conclusion                                                                                                                                                                                                                                                                     | 214                                                         |  |  |  |  |  |  |  |

| 7 | Eval | luation                                                                                                                                                                                                                                                                        | 215                                                         |  |  |  |  |  |  |  |

|   | 7.1  | Evaluation Platform                                                                                                                                                                                                                                                            | 216                                                         |  |  |  |  |  |  |  |

|   | 7.2  | Virtual Memory Operations - Map/Protect/Unmap 2                                                                                                                                                                                                                                |                                                             |  |  |  |  |  |  |  |

|   | 7.3  | Virtual Memory Operations - Appel-Li Benchmark                                                                                                                                                                                                                                 | 226                                                         |  |  |  |  |  |  |  |

|   | 7.4  | Dynamic Updates of Translation Tables                                                                                                                                                                                                                                          |                                                             |  |  |  |  |  |  |  |

|   | 7.5  | Scaling and Caching Performance                                                                                                                                                                                                                                    | 234                                           |  |  |  |  |  |  |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|--|--|--|--|

|   | 7.6  | Space and Time Complexity                                                                                                                                                                                                                                          |                                               |  |  |  |  |  |  |  |

|   | 7.7  | Correctness on Simulated Platforms                                                                                                                                                                                                                                 |                                               |  |  |  |  |  |  |  |

|   | 7.8  | Conclusion                                                                                                                                                                                                                                                         | 242                                           |  |  |  |  |  |  |  |

|   |      |                                                                                                                                                                                                                                                                    |                                               |  |  |  |  |  |  |  |

| 8 | Cone | clusion and Future Directions                                                                                                                                                                                                                                      | 245                                           |  |  |  |  |  |  |  |

|   | 8.1  | Conclusion                                                                                                                                                                                                                                                         | 245                                           |  |  |  |  |  |  |  |

|   | 8.2  | Future Work8.2.1Model Improvements8.2.2Implementation in a Monolithic OS Kernel8.2.3Towards Correct-by-Construction Address Spaces8.2.4Integration with Other Models8.2.5Applications to Other Areas of Operating Systems8.2.6Application to Network Configuration | 247<br>247<br>250<br>250<br>253<br>254<br>255 |  |  |  |  |  |  |  |

### Bibliography

263

# 1

# Introduction

This dissertation applies formal methods to the design and implementation of memory management and authorization components in operating systems. It uses a formal model to capture the complexity of memory addressing on modern hardware and adopts the principle of least-privilege to configure address translation hardware.

The principal goals of the formal model and its application in the context of system software are the following:

- 1. Provide an accurate representation of the memory subsystem of any hardware platform as seen by system software including nonuniform and heterogeneous translations and memories.

- 2. Establish a sound foundation to unambiguously name memory resources and to formally reason about address resolution.

- Enable the implementation of system software components to correctly manage memory resources and configure translation hardware.

- 4. Define and identify the semantics of address space configuration and the required authority to do so.

- 5. Apply the principle of least-privilege to the task of address space configuration.

The remainder of this chapter sets the stage for the work presented in this thesis by providing the motivational aspects followed by the problem statement and the contributions of this dissertation to systems research. Finally, an overview of the structure of the thesis is presented.

# 1.1 Motivation

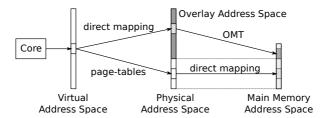

While application processes generally run in user space and in their own virtual address space, it is the task of system software (e.g. the operating system kernel) to provide this illusion of a uniform, linear address space to the application. Likewise, the kernel also runs in its own, linear address space separated from user space processes. To uphold this illusion, system software needs to correctly program the relevant translation units (e.g. the processor's memory management unit (MMU)). This in turn, requires system software to know the corresponding address a memory resource (e.g. DRAM or memory mapped device registers) appears on the processor's system bus.

The actual location of memory resources and devices, especially under which address they appear, depends on the current hardware configuration of the platform at hand where the configuration refers to the hardware components, their interconnection and state. Two platforms can have a very different configuration, especially for system-on-a-chip (SoC) architectures. Worse, the observed address ranges differ between two distinct cores, most prominently between the CPU and a direct memory access (DMA) capable device. This inherent heterogeneity, not only between two different platforms but also within a single platform, makes the design and implementation of system software tedious and error prone: writing to the wrong device register or accessing the wrong memory location can lead to data corruption, unexpected behavior, or security vulnerabilities.

While one may argue that the platform configuration information is passed to the operating system through UEFI [UEF17], ACPI tables [UEF15], those services are in fact other instances of system software and therefore need to know the locations of the resources present on the platform. DeviceTrees [dev17] on the other hand are a file format than a topology description and are incapable of expressing complex address typologies.

Moreover, UEFI services may not be present at all. A machine can be booted in legacy mode, or there is simply no UEFI available for that platform. Tiano Core [Tia19], for instance, is compiled for a specific platform including all information about memory and devices compiled into the UEFI image.

In summary, the hardware representation is, in some sense, too abstract which hides important details such as the actual topology, interconnect configurations, and locations of hardware firewalls. Moreover, this can be misleading. For instance, a resource access can have different characteristics from where it is accessed from (processor, device, accelerators, etc.), and this resource may actually have different addresses it appears.

The misleading abstractions need to be replaced with a more accurate representation, which reveals enough details of the underlying hardware with its configuration and characteristics to give system software a chance to actually handle and configure hardware correctly.

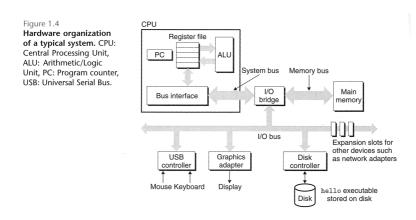

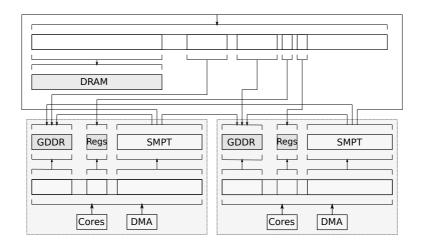

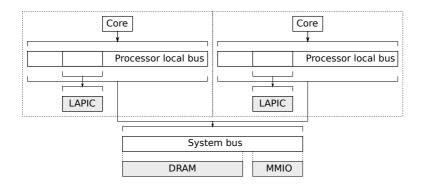

Therefore, system software needs to be written with an accurate description of the platform at hand, including the memory topology, addresses and sizes of memory resource and devices as seen from a particular core. Yet, the platform architecture diagrams presented in recent textbooks about operating systems (an example is shown in Figure 1.1) completely ignore the possibility of heterogeneity and different observed address ranges

#### Chapter 1 - Introduction

systems, but all systems have a similar look and feel. Don't worry about the complexity of this figure just now. We will get to its various details in stages throughout the course of the book.

Figure 1.1: System Architecture as presented in *Computer Systems, A Programmer's Perspective* by Randal E. Bryant and David R. O'Hallaron [BO15]. between two distinct cores. Hence, the diagrams shown are oversimplified and inaccurate, one may even say plain wrong.

Another aspect why an accurate representation of the hardware platform is system software verification. Correctness is a central property for system software and one way to guarantee correct operational behavior is through verification (e.g. seL4 [Kle+09] or CertiKOS [Gu+16]). While these projects prove or certify correct operational semantics with respect to an execution model, the proofs are based on an abstract machine representation, which is again greatly simplified and does not accurately represent the complexity and heterogeneity of a real system.

Instead of applying heuristics and using vague assumptions to configure translation units and abstract hardware as seen by software, this dissertation presents a sound and well-founded formal model to express the hardware configuration of computing platforms as a network of address spaces. This provides system software with enough details about the hardware to enable system software to correctly manage and configure the resources of a hardware platform.

## **1.2 Problem Statement**

This dissertation investigates the following research questions and problems from the angle of systems software.

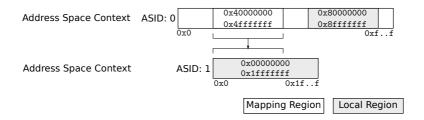

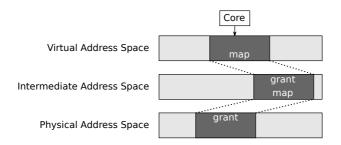

**Multiple-Physical Address Spaces** This thesis makes the case that the presence of a single, globally uniform physical address space has always been an illusion, and promotes the address space as a first-class abstraction to express the configuration of a platform. Processor cores and DMA-capable devices have different *views* of the platform: within a single address space, memory resources can appear at different addresses, they can be aliased or the same address refers to a different resource in two distinct address spaces. There is no longer *the (unique) physical address* of a memory resource. It is rather a question of what the set of addresses is

this memory resource appears at, and in which address spaces, or whether the same address in two address spaces really refer to the same resource. Getting this wrong leads to correctness problems, e.g. because of the misinterpretation of the address, software accesses the wrong underlying resource, which results in data corruption or information leakage.

**Platforms as a Network of Address Spaces** This dissertation argues that the configuration of a platform can be expressed as a network of address spaces which can be overlapping, isolated or intersecting in arbitrary ways. The connections between address spaces can be fixed or configurable. These aspects are hidden in the current hardware abstraction model. The dissertation explores a variety of platform architectures of different types and sizes. It further shows the applicability of a network of address spaces to express the configuration of the various platforms. This reveals important details of the underlying hardware and its characteristics to system software.

**Decoding Net Model of Address Spaces** The thesis shows that the network of address spaces can be formally specified as a decoding network. The *Decoding Net* is a directed graph of nodes corresponding to address spaces of a platform, while edges are mappings of addresses between two address spaces. This dissertation demonstrates that this formal specification is capable of accurately expressing inherently complex and heterogeneous platforms and execution modes of processors. Moreover, it is possible to define transformations on the *Decoding Net* without changing the *view* from within a particular address space. Lastly, the abstract *Decoding Net* can be refined to express existing hardware devices such as translation lookaside buffers (TLBs), memory management units, memory controllers and lookup tables.

Authorization and Configurable Decoding Nets The Decoding Net model captures a snapshot of the system configuration. This thesis further shows how the Decoding Net model can be extended with a notion of configuration and authorization using a least privilege approach. The central question is "who can configure this translation hardware and what rights does one need to have to do so?". The dissertation addresses this question by applying a fine-grained decomposition of the address translation configuration process into subjects, objects and the necessary authority on top of the *Decoding Net* model.

A Fast Implementation of the Authorization Model The thesis demonstrates that it is possible to efficiently implement the fine-grained authorization model following the principle of least-privilege plus the detailed address space model in an operating system. To do so, the thesis presents an operating system architecture that separates low-level protection primitives from high-level policy mechanisms to manage memory resources and configure address translation units.

## **1.3 Structure of the Dissertation**

**Chapter 2** provides background information on the definitions used for addresses and address spaces in hardware manuals, and a survey of real and proposed hardware translation schemes. It then presents the current abstractions used by operating systems and highlights the problems that arise with respect to the presented address translation schemes and platforms.

**Chapter 3** surveys work related to memory management and abstractions used in operating systems, runtimes for scheduling and memory allocation policies, and models of processor and the semantics of memory accesses.

**Chapter 4** presents the address space model to capture the complexity of the memory topology of any platform. Moreover, it defines the Decoding Net, a formalization of the address space model in Isabelle/HOL which rigorously specifies the semantics of address decoding, and defines correct transformation algorithms on top of the model. This is joint work with David Cock (who significantly helped with formalizing the address space model), Lukas Humbel, Gerd Zellweger, Kornilios Kourtis, Timothy Roscoe, and Dejan Milojicic and it appeared in related publications [Ach14; Ger+15; Ach+17b; Ach+18].

**Chapter 5** extends the decoding net model of Chapter 4 to add support for dynamic address spaces in both their translation configuration and the total number thereof. The chapter further presents a fine-grained authorization model for configuration changes. This is based on joint work with Nora Hossle (who implemented the executable specification), Lukas Humbel, Daniel Schwyn, David Cock and Timothy Roscoe in *Least-Privilege Memory Protection Model for Modern hardware* [Ach+19a] and [Hos19].

**Chapter 6** describes the needed mechanisms for an efficient implementation of the address space model of **Chapter 5** in operating system software. The chapter presents *Barrelfish/MAS*, an extension to the Barrelfish research operating system that implements the address space model following the principle of least-privilege for translation configuration. This is based on joint work with Nora Hossle, Lukas Humbel (who contributed significantly to the runtime representation), Daniel Schwyn, David Cock and Timothy Roscoe in *Least-Privilege Memory Protection Model for Modern hardware* [Ach+19a].

**Chapter 7** evaluates the implementation of *Barrelfish/MAS* in the context of memory management, least-privilege address translation configuration, scaling and bookkeeping overheads. This is based on joint work with Nora Hossle, Lukas Humbel, Daniel Schwyn, David Cock and Timothy Roscoe in *Least-Privilege Memory Protection Model for Modern hardware* [Ach+19a].

**Chapter 8** draws the conclusions of this dissertation and presents future directions of the address space memory model and its applications in system software.

### **1.4 Related publications**

This dissertation presents work that is part of the Barrelfish research operating system (http://www.barrelfish.org). Many people have contributed to the existing infrastructure and the Barrelfish ecosystem, which enabled the research of this dissertation.

The following list provides references to work presented in this dissertation, which is published in some form.

- [Ach14] Reto Achermann. "Message Passing and Bulk Transport on Heterogenous Multiprocessors". Master's Thesis. Department of Computer Science, ETH Zurich, 2014.

- [Ach+17b] Reto Achermann, Lukas Humbel, David Cock, and Timothy Roscoe. "Formalizing Memory Accesses and Interrupts". In: Proceedings of the 2nd Workshop on Models for Formal Analysis of Real Systems. MARS 2017. 2017.

- [Ach+18] Reto Achermann, Lukas Humbel, David Cock, and Timothy Roscoe. "Physical Addressing on Real Hardware in Isabelle/HOL". in: Proceedings of the 9th International Conference on Interactive Theorem Proving. ITP'18. 2018.

- [Ach+19a] Reto Achermann, Nora Hossle, Lukas Humbel, Daniel Schwyn, David Cock, and Timothy Roscoe. A Least-Privilege Memory Protection Model for Modern Hardware. 2019. arXiv: 1908.08707 [cs.0S].

- [Bau+09a] Andrew Baumann, Paul Barham, Pierre-Evariste Dagand, Tim Harris, Rebecca Isaacs, Simon Peter, Timothy Roscoe, Adrian Schüpbach, and Akhilesh Singhania. "The Multikernel: A New OS Architecture for Scalable Multicore Systems". In: *Proceedings of the ACM SIGOPS 22nd Symposium on Operating Systems Principles.* SOSP '09. 2009.

- [Ger+15] Simon Gerber, Gerd Zellweger, Reto Achermann, Kornilios Kourtis, Timothy Roscoe, and Dejan Milojicic. "Not Your Parents'

Physical Address Space". In: *Proceedings of the 15th USENIX Conference on Hot Topics in Operating Systems*. HOTOS'15. 2015.

- [Ger18] Simon Gerber. "Authorization, Protection, and Allocation of Memory in a Large System". PhD thesis. ETH Zurich, 2018.

- [Hos19] Nora Hossle. "Multiple Address Spaces in a Distributed Capability System". Master's Thesis. Department of Computer Science, ETH Zurich, 2019.

- [Sch17] Daniel Schwyn. "Hardware Configuration With Dynamically-Queried Formal Models". Master's Thesis. Department of Computer Science, ETH Zurich, 2017.

# 2

# **Problem Statement**

This chapter makes the case for a new model for representing and interpreting physical addresses in a machine for the purposes of memory management and memory subsystem configuration. Secondly, it presents a survey of some of the many violations of these assumptions in past, current, and proposed future hardware. Moreover, it points to the challenges this creates for effective management of physical memory as a resource in systems software.

# 2.1 Motivation

To this day, hardware designers have come up with many memory address translation schemes among which page-based virtual memory [Den70]

and virtualization [PG74; Int19a] being one of the most ubiquitous. Each address translation scheme has different features, translation granularity, and means of configuration. The common denominator of those translation mechanisms is that system software is responsible for *correctly* configure them. Failing to do so leads to severe problems such as algorithms producing the wrong results, data corruptions, information leakage, crashes and security vulnerabilities.

The objective of this chapter is to demonstrate the existing mismatch between the hardware abstractions and assumption about the memory system used in operating systems today on the one hand, and the architecture and configuration of real hardware as it is seen by software running on the platform on the other hand. This mismatch is a problem. It has lead to various security vulnerabilities and bugs in system software (Section 2.4.2) e.g. 33% of code-changes to the Linux memory manager are bug fixes [HQS16].

The chapter is structured as follows:

- 1. Section 2.2 presents a survey of real and proposed memory address translation hardware components including their translation and configuration mechanisms.

- 2. Section 2.3 describes the "single global physical abstraction".

- 3. Section 2.4 shows the problems that arise with the abstractions currently used by operating system and actual memory subsystem of the hardware platforms presented in the survey.

- 4. Section 2.5 analyzes the implications of this mismatch for operating system design and implementation.

# 2.2 Survey of Memory Address Translation

With virtual memory [Den70] and virtualization in general [PG74], processing units, processor cores or DMA-capable devices, only ever deal

with an opaque handle (the virtual address) to the physical resources it accesses. This is one of the corner stones of computing, providing isolation and protection between two tasks running on the same machine.

Processes and even operating systems in virtual machines are given the impression of being the only task or operating system running on the machine providing the illusion of having exclusive access to all resources, sometimes even more resources than exist in reality (e.g. demand paging [Fot61]). This illusion, however, does not stop at the physical machine level: in memory-centric computing [Far+15; Bre+19] there is more memory available than the machine can ever issue addresses for. Therefore, only a configurable subset can be accessed at the same time.

In summary, there are multiple types of addresses (the most prominent of which are virtual and physical addresses), and hardware translates them using different translation schemes configured by system software.

The remainder of this section analyses the terminology of memory addresses used in technical reference manuals (Section 2.2.1) and then presents a survey of memory translation mechanisms, either present in existing, real hardware (Section 2.2.2), or proposed as part of conference submissions or white papers (Section 2.2.3). This provides an overview of the complexity of memory translation schemes.

### 2.2.1 Address Spaces and Address Definitions

In technical reference or software developer's manuals, hardware vendors describe the features of their products and how to use them. To avoid confusion, the manuals include a section or table about the used terminology. The purpose of this section is to compare the definitions and terminologies of different kinds of address and address spaces found in those documents. The address type and its context are important to precisely refer to a resource in the system e.g. a device virtual address might be different to a guest virtual address.

| ı            | ı              | I/O virtual | DMA | guest virtual   | guest physical        | I               | host physical | effective | logical   | virtual          | linear           | physical                | Intel            |

|--------------|----------------|-------------|-----|-----------------|-----------------------|-----------------|---------------|-----------|-----------|------------------|------------------|-------------------------|------------------|

| local memory | device virtual | ı           | ı   | guest virtual   | guest physical        | system physical | host          | effective | logical   | virtual = linear | virtual = linear | physical                | AMD              |

| ·            | virtual        | virtual     | ·   | virtual         | intermediate physical | ı               | physical      | ·         |           | virtual          |                  | physical / intermediate | ARM              |

| I            | effective      | I           |     | fully qualified | guest real            |                 | host real     |           | effective | I                | virtual          | real                    | <b>IBM Power</b> |

Table 2.1: Summary of Different Address Terminologies Found in Hardware Manuals.

Table 2.1 summarizes the address types. A row corresponds to set of terms used by different vendors referring to *similar* concepts.

**Intel Terminology** The Intel 64 and IA-32 Architectures Software Developer's Manual [Int19a] and the Intel Virtualization Technology for Directed I/O Architecture Specification [Int19b] describe multiple memory models and address types. Memory attached to a processor bus is referred to as *physical memory* and each byte of it assigned a *unique physical address*. The *physical address space* is then a range of addresses from zero to  $2^b - 1$  where *b* is the maximum supported address width. Itanium [Int10a] further introduced multiple virtual address space regions where the combination of them formed a large 85-bit *global* address space.

Physical memory is generally not accessed directly. The processor has three different memory models: flat, segmented, and real-address mode. The memory model defines how a *logical address* (segment selector + effective address) used by the processor is converted into a *linear address* (See Section 2.2.2.1 for an illustration).

The linear address is then translated to a physical address either through a one-to-one mapping or through a page-based translation mechanism (paging). Paging effectively virtualizes physical memory. Depending on its configuration, the linear address corresponds to the physical address (one-to-one mapping), or to the virtual address (with paging). An address is in its *canonical* form if the topmost (63 - b) bits are either all zero or all ones, with *b* being the number of bits implemented by hardware.

Virtualization partitions the machine and adds another layer of address types. The physical address above is now referred to *host physical address* and is defined as:

"Physical address used by hardware to access memory and memory-mapped resources." – Intel 64 and IA-32 Architectures Software Developer's Manual [Int19a]

System Software running inside a partition or virtual machine sees *guest physical addresses* and applications use *guest virtual addresses*. The

manual speaks about the *view* of physical memory in this context. Addresses used by software on the host processor are *virtual addresses*. Devices operate on *DMA addresses* which may refer to either a host/guest physical or virtual address, or an I/O virtual address.

**AMD Terminology** AMD uses almost identical terminology to Intel. The AMD64 Architecture Programmer's Manual [AMD19] makes an explicit association between *virtual* and *linear* addresses and the virtual address is translated into *physical* addresses through paging. Similarly, the logical address is then formed by a segment selector and an *effective* address.

The AMD I/O Virtualization Technology (IOMMU) Specification [AMD16] further defines a *device virtual address*, which is either a *guest physical* or a *host / system physical address*. The manual states that the host physical address is "*in most systems identical with the System Physical Address*". The *local memory address* is the device local physical address used to access device private resources, which may or may not be mapped into the system physical address space.

**Arm Terminology** The Architecture Reference Manual for ARMv8-A [ARM19a] describes the virtual memory system architecture for the 32-bit and 64-bit operating modes. It defines the *virtual address* as an address which is used in an instruction. Similar to the x86 canonical address, virtual addresses have the top bits either all ones or all zeroes.

The virtual address gets translated to an *intermediate physical address* which is the output address of the stage-one translation and the input address of the stage-two translation. The intermediate address then gets translated to a physical address, which corresponds to "*a location in a physical memory map.*" If there is just a single stage translation, then the intermediate address is identical to the physical address.

The Arm architecture further defines two address spaces that exist in parallel: secure and non-secure. This distinction provides a mechanism to isolate certain resources and devices from unprivileged accesses or interference. For instance, only software running in the secure world may access resources within the secure address space. Processors or devices make memory accesses either *secure* or *non-secure* [ARM09]. This implies:

"Secure 0x8000 and Non-secure 0x8000 are, technically speaking, different physical addresses" – ARMv8-A Address Translation [ARM17]

There are no special terms for System MMU [ARM16] (the Arm IOMMU equivalent). The same translation regimes as for processor cores are used.

**IBM Power Terminology** On the IBM POWER9 platform [IBM18; IBM17], threads use 64-bit *effective addresses* which are comprised of an effective segment identifier and offset to access different storage objects. The address is a *fully qualified address* if it also includes the *effective logical partition identifier* which uniquely identifies the processing thread.

The (process-local) effective address is translated to a 68-bit operating system global *virtual address*. The process addressing context, a segment descriptor defines this translation. The effective segment ID is converted into a virtual segment ID. Together with the offset, this virtual segment ID forms the virtual address. Lastly, the page-based translation mechanism converts the virtual address to a 56-bit *real address*. With virtualization enabled, a partition-scoped page table translates *guest real addresses* to *host real addresses*.

**Conclusion** Hardware vendors use similar terminology to refer to different address types (Table 2.1). Yet, there are subtle differences especially when referring to addresses a device is using. From the analyzed architectures, IBM Power diverges the most. The difference between virtual and linear addresses are vague, sometimes they are equivalent. Arm explicitly acknowledges the existence of multiple address spaces and AMD the presence of device private resources which may not be accessible from the main processor cores.

### 2.2.2 Translation Schemes in Real Hardware

Processors, interconnects and memory controller use different addressing modes requiring addresses of different types to be converted between one another. This section presents a survey of different translation schemes which various vendors have implemented in production hardware.

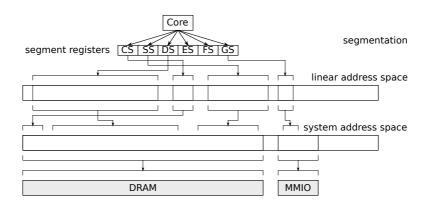

### 2.2.2.1 Segmentation

In segmentation-based memory systems [RK68] such as on x86 [AMD19; Int19a] or Power [IBM18], software accesses memory through *segments* that have a defined fixed or configurable size, protection attributes and map contiguously onto a linear address space. The remainder of this section focuses on the x86 architecture as an example of segmentation.

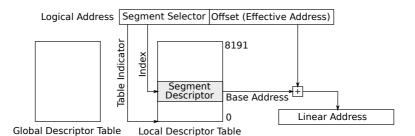

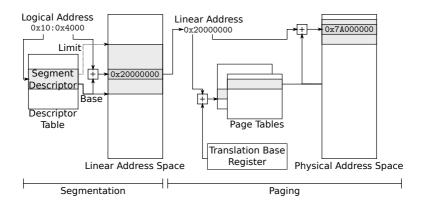

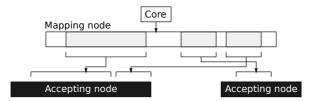

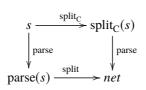

Figure 2.1: Logical to Linear Address Translation Using Segmentation on the x86 Architecture [Int19a].

Figure 2.1 illustrates the conversion of a logical address to a linear address using segments on the x86 architecture. The logical address consists of a segment selector and an offset into the segment (or effective address), combined using the colon as visualization.

The segment selector indicates whether to use the global or local descriptor table and specifies the segment descriptor by an index into the table. The descriptor tables are stored in memory. The segment descriptor stores the base and limit of the segment. The linear address is then calculated by adding the offset (effective address) to the segment's base address.

### Linear Address = Segment Base Address + Effective Address

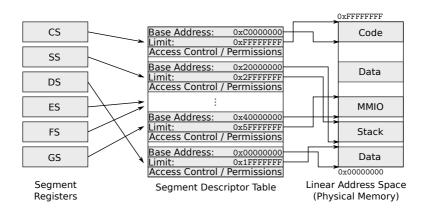

There are six segment registers available on the x86 architecture to speed up the translation process by storing an entry of the descriptor table. Their name indicate their historic usage: CS (Code Segment), SS (Stack Segment) and four data segments DS, ES, FS, GS. Their use depends on the processor mode and the segmentation model. Segments can have an intended use e.g. code, data and stack. Data can be accessed explicitly by stating the segment e.g. DS:0x1000 or implicitly e.g. through an instruction fetch or stack operations. The x86 architecture offers three segmentation models.

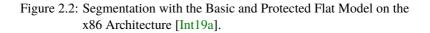

**Basic and Protected Flat Models** The basic flat model is arguably "*the simplest memory model*" [Int19a] which effectively enables access to a contiguous, linear address space by hiding segmentation as much as possible. There are two segment descriptors required, one for code and one for data segments as illustrated in Figure 2.2. Both descriptors are set up to map the entire linear address space including regions which are not backed by physical resources like RAM or memory-mapped device registers. The processor can therefore access and execute from every memory location including modification of its own code.

The protected flat model sets the base and limits of the segment descriptors to match the actual physical resources present in the machine. Accesses to non-existing memory resources are now caught by the segment limits and trigger a general protection fault.

**Multi-Segment Model** The basic models above do not enforce separation of code, stack and other data structures. The multi-segment model enables the use of all six segments. Each process has its own descriptor

(b) Protected Flat Model.

Figure 2.3: Segmentation with the Multi Segment Model on the x86 Architecture [Int19a].

table and uses different segments for code, stack and data which have different access protections e.g. a process cannot modify its own code. Figure 2.3 illustrates the use of multiple segments and how they are mapped onto the linear address space.

**Segmentation with Paging** Segmentation can be used with and without a page-based translation mechanism. With paging, this results in a two-stage translation mechanism where a logical address is first converted into a linear address using segmentation. The linear address space is then split up into pages which map onto the physical address space. Each page translates a contiguous block of addresses. This translation is defined by an in-memory data structure (more about page-based translation schemes in Section 2.2.2.2). Figure 2.4 illustrates the combined translation mechanism with segmentation and paging.

**64-bit Operation Mode** During initialization, system software enables the 64-bit operation mode (AMD64 [AMD19; Int19a]) which mostly, but not completely, disables segmentation: limit checks in all segments are

disabled and the processor ignores segment bases for CS, DS, ES and SS and hard-wires them to zero. This results in a flat, 64-bit linear address space where the linear address is equal to the effective address.

The two exceptions are the FS and GS segment registers, which can still hold a value other than zero as base address. Software can use those two additional registers to hold pointers to local data structures, for instance.

### 2.2.2.2 Page-based Translation Mechanism

Page-based translation mechanisms, or paging for short, are widely used e.g. on x86 platforms [Int19a; AMD19], IBM Power [IBM18], ARMv7 and ARMv8 [ARM19a; ARM17] including virtualization, IOMMUs [Int19b; AMD16], and SMMUs [ARM16]. The next two paragraphs illustrate paging in the native and virtualized environments.

**Paging** Using paging, the virtual (or linear) address space is divided into naturally aligned pages of equal size, e.g. 4 KiB on x86. Depending on the architecture and processor, larger page sizes may be supported (e.g. 2 MiB

Figure 2.4: Segmentation with Paging on the x86 Architecture [Int19a].

large and 1 GiB huge pages on x86), Some other architectures like Intel Itanium [Int10a], Arm [ARM17] or MIPS R4600 [ITD95] support more page-sizes, including the size of the page tables themselves.

The translation is defined by an in-memory data structure called the page table which defines a mapping from virtual pages to physical frames. The page tables themselves operate on physical addresses. Each entry in the page table defines the target address, permissions, access characteristics and caching properties of a page of memory. Page-table entries may not always be strictly independent e.g. super sections on ARMv7 [ARM19a]. The page table is a multi-level radix tree where each level translates a portion of the linear address space.

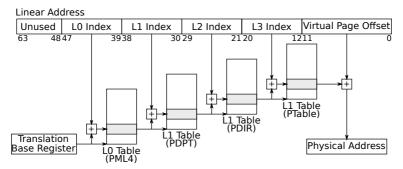

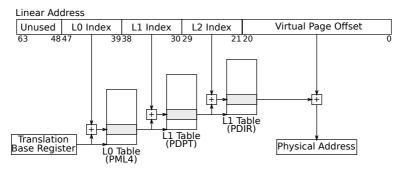

Figure 2.5 shows the translation of a linear address into a physical address using a multi-level page table for 4 KiB and 2 MiB pages. Translation starts at the translation base register (cr3 on x86), which serves as the base address of the top-level page table. Parts of the linear address define the indices into the different tables. For each level of the page table, the entry at the extracted index defines the base address of the next table. This process is repeated until the last level is reached. The frame base address of the entry is then added to the page offset to obtain the physical address. Using multi-level page tables, large and huge pages can be implemented by stopping the page-table walk early as shown in Figure 2.5b.

**Virtualization using Nested-Paging** A virtual machine [PG74; Gol73], emulates a computer system with a defined configuration (CPUs, memory, devices) on top of a physical machine. Virtual machines allow running multiple operating systems on the same server. Using special hardware extensions (e.g. in the processor [Uhl+05]), memory accesses in virtual machines are translated twice. From guest virtual to guest physical to host physical addresses, or virtual-intermediate-physical using ARM terminology for two-stage translations (Recall Section 2.2.1). Each translation stage itself is defined by a page-table structure. The first stage is managed by the guest operating system, and the second stage by the hypervisor or virtual machine monitor using "extended page tables (EPT)".

(a) Linear to Physical Address Translation with 4 KiB Page Size.

(b) Linear to Physical Address Translation with 2 MiB Large Page Size.

# Figure 2.5: Illustration of a Linear to Physical Address Translation Using a Multi-Level Page Table [Int19a].

Figure 2.6: Illustration of a Two-Stage Guest-Virtual to Host-Physical Translation with Nested Paging on the x86 Architecture [Int19a].

The guest page tables contain guest physical addresses. Therefore, for each translation step the EPT needs to be walked to obtain the physical address of the next page table.

### 2.2.2.3 Translation Lookaside Buffers (TLB)

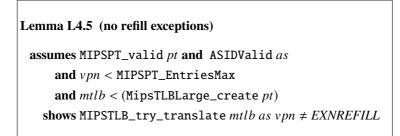

Translating addresses using a full page-table walk results in up to four memory accesses in the native case and up to 24 memory accesses using nested paging. Recall,page tables operate on physical addresses themselves [Int19a; ARM17; AMD19], and hence those memory accesses are physical addresses and do not need to be translated. Consequently, translating an address using a multi-level page table is expensive [Bas+13]. TLBs cache successfully translated addresses to reduce the number of page-table walks required. Consequently, a TLB holds a subset of the translations defined by the page table. Section 4.6 will present an operational model of a software-loaded TLB.

In the event software issues an address which is not present in the TLB, a page-fault exception is triggered. Either the operating system (in the case of a software-loaded TLB), or a hardware page-table walker reads the page table and updates the cache with the new translation. This results in additional memory accesses to translate a linear to a physical address.

TLBs are a cache, which the operating system needs to keep consistent with the backing page table. To make updates to the page table visible to software, existing entries must either be explicitly updated, or invalidated and the hardware page-table walker fetches the new translation from the updated page table.

### 2.2.2.4 Register-Based Lookup Tables

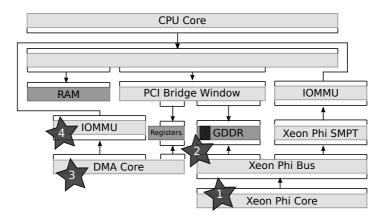

Page-based translation schemes do not have to use multi-level, in-memory page tables: if the number of pages is small enough, an array of registers may be sufficient to configure the translation. An example of such a lookup table is the system memory page table (SMPT) of the Intel Xeon Phi co-processor [Int14a] or the Intel Single-Chip Cloud Computer (SCC) [Int10b].

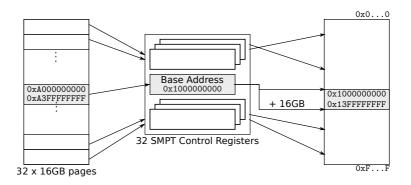

The system memory page table (SMPT) translates addresses from a 512 GiB region in the 40-bit Xeon Phi address space to the 48-bit system address space (possibly protected by an IOMMU).

Figure 2.7 illustrates this translation. The lookup table consists of 32 registers each controlling how a 16 GiB "page" is being translated. There exists a fixed relationship between the register and the region of co-processor physical addresses controlled by the register. Any 16 GiB aligned target address is possible. In contrast to the page tables, an entry of the SMPT cannot be invalidated, it always translates somewhere.

Similarly, the SCC has a 256-entry lookup table each mapping a 16 MiB physical memory frame in the processor's 32-bit address space to the extended memory map of the system. More on SCC memory addressing in Section 2.2.3.1.

Figure 2.7: The System Memory Page Table on the Intel Xeon Phi Co-Processor.

### 2.2.2.5 Fully Associative Lookup Table

One way to interpret the SMPT is like a "*direct mapped*" translation cache: each entry of the SMPT holds the translation for one specific, fixed page of memory. On the other side of the spectrum, a *fully associative* translation cache decouples the entry from the memory page it translates, while N-way set associative caches are in between.

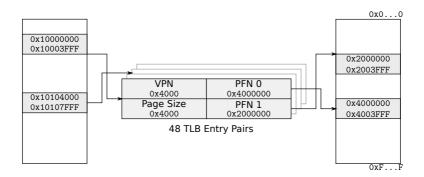

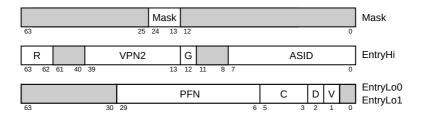

The MIPS R4600 TLB [ITD95] is an example of a fully-associative lookup table. It is a software-loaded, fully associative TLB with 48 entry-pairs. The translation scheme is illustrated in Figure 2.8 and further used as an example in Section 4.6. Note, that some TLBs implement a multi-level caching scheme and are N-way set associative.

Figure 2.8: Fully Associative, Software Loaded Translation Lookaside Buffer.

Each entry of the MIPS R4600 TLB maps two consecutive pages of virtual memory to two independent physical memory frames. Each entry can map *any* virtual page to *any* physical frame. In theory, it is possible to have two entries translate the same virtual page which leads to undefined behavior and possibly damage the chip [ITD94].

### 2.2.2.6 Multi-Stage Translation Schemes

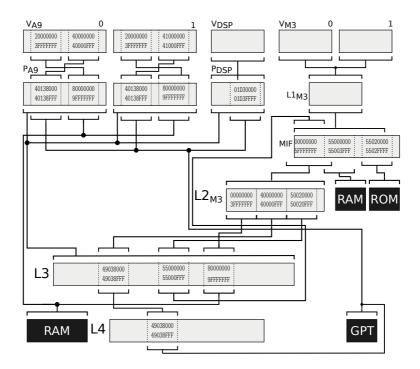

Memory addresses might be translated multiple times while a memory request traverses the network of interconnects in the system. Examples of this include the memory controller on multi-socket x86 machines, accesses to the host DRAM from the Intel Xeon Phi co-processor (Section 5.5), and the ARM Cortex-M3 Subsystem on the Texas Instruments OMAP4460 [Tex14].

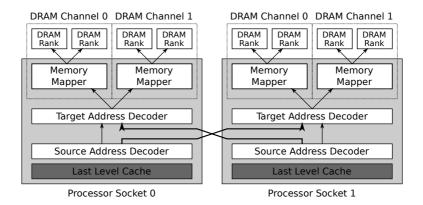

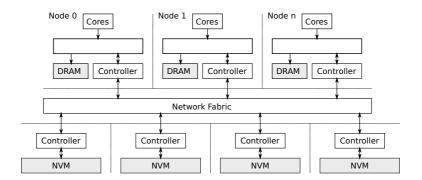

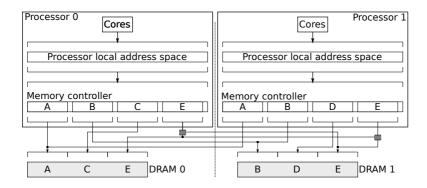

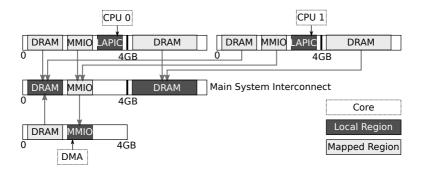

**Memory controllers and multi-socket machines** Large server machines consist of multiple processors each having a collection of cores. Each processor has memory controllers with DRAM memory attached (Figure 2.9). The memory access characteristics of such a machine are non-uniform, or NUMA [Lam13] for short, where accesses to a processor's local memory is faster than accessing memory attached to another processor [Gau+15; Kae+15].

Memory controllers of modern processors are configurable. However, there exist hardly any public documentation on the multi-stage translation and for-

warding process of memory controllers. Nevertheless, reverse engineering efforts can reveal the translation scheme and register descriptions [Hil17; Hil+17].

The BIOS (firmware initializing hardware during boot) might display an option to select the visibility of the NUMA topology to the operating system. This corresponds to partitioning of memory into the NUMA regions, or striping among all NUMA nodes at cache-line granularity. The system software can configure the memory controllers using memory mapped registers where each socket can be configured individually.

Figure 2.9 depicts the address translation scheme of Intel Xeon processors of the Haswell and Broadwell generations based on the description in [Hil17; Hil+17]. Note, that the address decoding happens after the last-level cache and therefore in *physical addresses*. The translation is triggered when a memory access fetches data from DRAM. The steps are as follows:

- 1. The source address decoder forwards the request to the memory controller of the target NUMA node depending on the physical address of the memory access and the configuration of the source address decoder.

- 2. The target address decoder forwards the requests to the memory mapper of the correct DRAM channel. While doing so, the target address decoder converts the physical address from the system address to the mapper-local address space. Again, this depends on the configuration and the physical address.

- 3. The memory mapper forwards the request to the corresponding DRAM rank, as defined by its configuration. Again, this converts the address into the DRAM rank local representation.

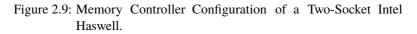

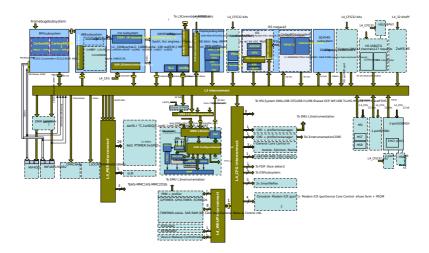

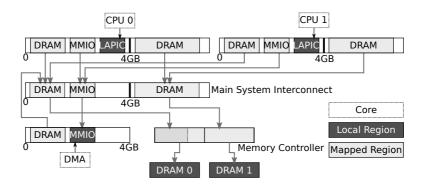

**Secondary Translations on the Ti OMAP 4460** The ARM Cortex-M3 subsystem of the Texas Instrument OMAP 4460 [Tex14] presents an interesting case: the two ARM Cortex-M3 cores share a two-stage MMU setup as shown in Figure 2.10. The MMUs of the Cortex-M3 cores are

configured from the Cortex-A9 processor on the OMAP 4460 through a dedicated configuration port.

The shared L1 MMU translates memory requests and forwards them to the L2 master interface (L2 MIF). This acts as an address splitter, forwarding requests either to the local RAM, ROM, or to the second-stage translation unit (L2 MMU, on Figure 2.10) which translates the address and routes the request to the L3 interconnect. This makes other system resources such as RAM accessible to the Cortex-M3 core.

The interesting case, however, is when the L2 MMU emits an address to the L3 interconnect, which falls into the address range of the L2 MPORT. This creates a cycle: L2 MIF-L2 MMU-L3 interconnect-L2 MIF. Note, a similar cycle exists on the Intel Xeon Phi co-processor. In both instances, they are benign.

Figure 2.10: Texas Instruments OMAP4460 Cortex-M3 Subsystem.

### 2.2.2.7 System on a Chip Firewalls

SoC platforms are networks of components which are connected through interconnect networks and buses. Firewalls mediate access from and to hardware components connected to a bus or interconnect. Based on in-band attributes including the request type (read/write), and connection identifiers for example, the firewalls of the Texas Instruments OMAP 4460 [Tex14] can block or allow access to an entire subsystem.

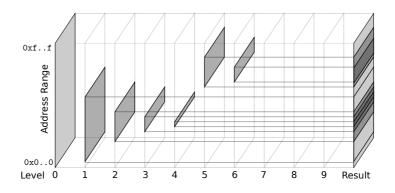

The firewall is region based, where each region has a start and end address, an assigned priority level, and can have different access permissions. Regions with a higher priority take precedence over lower priorities. Figure 2.11 illustrates a firewall configuration using regions with different priorities shown as levels in the figure. The regions are then projected on one another onto the result plane.

Figure 2.11: Address Filtering in the Firewalls on the Texas Instruments OMAP 4460 [Tex14].

### 2.2.2.8 IOMMU / System MMU

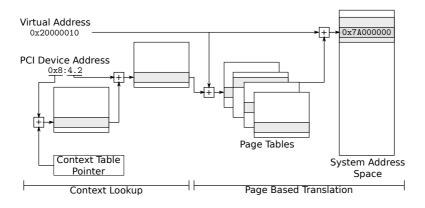

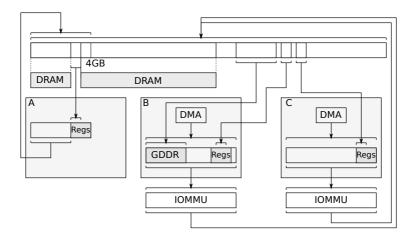

IOMMUs or System MMUs translate memory requests coming from I/O devices. This effectively restricts the resources a device can access e.g. which RAM regions it can write to. IOMMUs are often configured using the same paging-structure to configure the translations as processor cores use for paging [Int19b; AMD16; ARM16]. In contrast to a processor core, there might be *multiple* devices covered by a single IOMMU which

maintains a context per device. This context then contains a pointer to the root-level page table to be used to translate requests from this device. Similar to "normal" paging, IOMMU also support virtualization using nested paging. Figure 2.12 shows an illustration of the translation process.

The IOMMU then selects the context based on the *source* from which the memory request comes from. This source might be, for example, the PCI bus-device-function triple contained in the PCI transaction. Consequently, even though two devices access the same address, they can get translated differently by the IOMMU.

Figure 2.12: Example of a Translation Scheme of an IOMMU Based on Intel VT-d [Int19b].

### 2.2.2.9 Enclaves

Applications running on an operating system or virtual machines running in the cloud are isolated from each other through hardware mechanisms such as virtual memory. However, they have to trust the operating system, hypervisor or cloud vendor not to interfere with the integrity and confidentiality of their data. Hardware mechanisms such as the Intel Software Guard Extensions [Int19a] (SGX) are designed to prevent the operating system or hypervisor from accessing application data (e.g. [Fer+17; BPH15]) through memory isolation and encryption. This enclave "*is a protected area in the application's address space, which provides confidentiality and integrity even in the presence of privileged malware.*" [Sel16]. However, information may still be leaking out of the enclave through side channels [Van+18].

The Intel Software Guard Extensions (SGX) [Int19a] explicitly assigns memory to the Enclave Page Cache (EPC) to make it accessible to the enclave. Memory accesses to a page of the EPC is subject to additional hardware access control checks e.g. from within an enclave, code cannot be loaded from outside the enclave, and access to pages in the EPC from outside the enclave results in undefined behavior. Normal protection such as paging and segmentation are still effective as the enclave effectively runs with the linear address space of a user-level process.

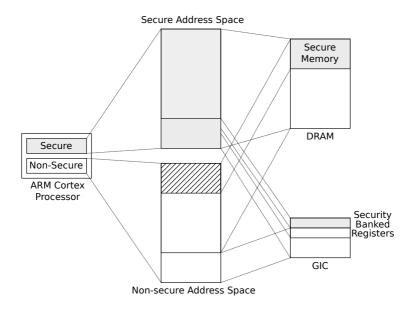

### 2.2.2.10 ARM TrustZone

Recall, ARM-based platforms that implement TrustZone [ARM09] split the memory subsystem into two: a *secure* world and a *non-secure* world. Effectively the "*ARM architecture defines two physical address spaces*" [ARM17]. Memory, devices and processors can be assigned to either the secure or non-secure world. Some of which are capable of being in both, or switch between worlds by changing the operation mode (e.g. secure monitor calls on the Cortex processors)

Figure 2.13 illustrates a simplified setup with one ARM Cortex processor, some DRAM and a device – the generic interrupt controller (GIC). A portion of DRAM is *configured* to be secure memory and hence only accessible from secure devices or processors. Similarly, the GIC is TrustZone-aware and some of its registers are "*security banked*" meaning despite being located at the same address, a different register is accessed depending on whether the access originated from the secure or on-secure world. A formalization of TrustZone revealed several imprecise or ambiguous specifications [Arc19].

Figure 2.13: Two Physical Address Spaces in ARM TrustZone.

The processor can operate in secure and non-secure mode which changes the view of the world: only in the secure mode, the processor is able to access the secure memory region.

### 2.2.3 Proposed Translation Schemes

The implementation of address translation schemes usually involves tradeoff decisions such as the granularity of protection and translation vs. required resources to configure how hardware translates addresses. This section surveys improvements and alternatives to the translation schemes described in the previous section and prototype hardware.

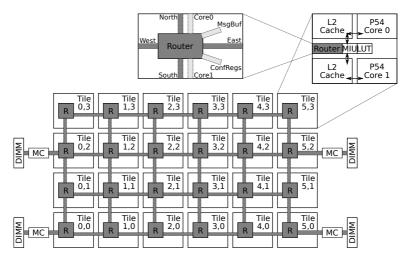

### 2.2.3.1 Intel's Single-Chip Cloud Computer

The Intel Single Chip Cloud Computer (SCC) [Int10b] consists of 24 tiles with two Pentium cores each. The tiles form a two-dimensional mesh structure where each tile can be identified using its (x, y)-coordinates. Figure 2.14 on page 37 illustrates the top-level layout of the chip. The architecture has four memory controllers (MC) that allow up to 64 GiB of DRAM. In addition, each core has private, on-die memory for message passing buffer (MBP) and system configuration space.

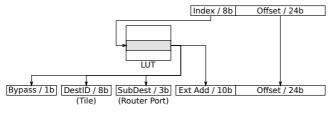

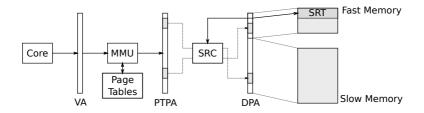

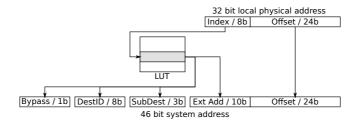

The cores operate as normal Intel Pentium processors including segmentation and paging as described earlier. Logical and linear addresses are translated to (core-local) physical addresses. Upon a miss in the core's L2 cache, the request is forwarded to the mesh interface unit (MIU) on the tile which then consults the system address lookup table (LUT) to obtain the destination tile of the request.

The memory request is then forwarded to the destination tile using the routing network. The router in the destination tile forwards the request to the sub-destination ID passed as part of the address. The bypass bit indicates whether to bypass the mesh interface unit to access the tile-local memory buffer directly. Each core having its own lookup table and configuration registers being memory mapped, it can be configured such that the core is completely sequestered and cannot change its own lookup table, which defines what resources the core can access.

### 2.2.3.2 Reducing TLB Miss Overheads

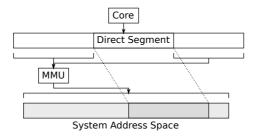

Big-memory workloads experience a high TLB misses rate resulting in overheads due to walking the page-table structures. This is a problem as such workloads end up spending 50% or more of their clock cycles handling TLB misses [Bha17], while at the same time those workloads seldom use the rich features provided by page-based virtual memory. Direct Segments [Bas+13] map a part of the linear address space using segmentation-based technique, while mapping the remaining part of the

(a) SCC Top-level Tile Network.

(b) Local to System Address Translation on the SCC.

Figure 2.14: Memory Addressing in the Intel Single-Chip Cloud Computer (SCC).

linear address space using page-based virtual memory translation (Figure 2.15).

Figure 2.15: Illustration of a Direct Segment Mapping.

This effectively preempts the page-table walk, similar to large-pages which may not necessarily be good in NUMA systems because of memory access imbalances causing memory controller congestion [Gau+14]. The overhead of radix-tree based virtual memory translations can be reduced by leveraging application specific translation schemes and exposing physical memory resources to applications [Ala+17]. The direct segment approach is also applicable in the virtualized case where it can reduce the full nested page-table walk to two direct segment translations [Gan+14]. Range Translations [Gan+16] and redundant memory mappings [Kar+15] added support for multiple ranges or segments to be mapped. Those approaches speed up translations at the cost of coarse-grained protection and requirement of large, contiguous blocks of 'physical' memory. Agile paging [GHS16] combines nested page-table walks and shadow-paging to reduce overheads of 2D page-table walks and virtual machine monitor involvement in page-table updates. Those proposals effectively carve out a contiguous region of memory which is translated differently. Devirtualized memory [HHS18] tries to identity-map memory to avoid virtual to physical translations by leveraging permission validation techniques [KCE92; WCA02].

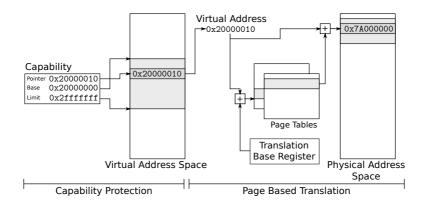

### 2.2.3.3 Hardware Capabilities

Page-based virtual memory introduces a tradeoff between translation and protection: while the use of large and huge pages speed up TLB misses by cutting page-table walks short, the protection granularity is coarser grained as a result. Instruction set capabilities such as CHERI [Woo+14] or "Matching Key Capabilities" [Ach+17a; Azr+19; Bre+19] separate translation from protection as illustrated in Figure 2.16. To some extent, this adds a segmentation-like layer on top of the virtual address space, where the segment descriptor is encoded into the hardware capability. The set of physical resources that are accessible is defined by the combination of the capability protection and the virtual memory translation.

Figure 2.16: Hardware Capabilities used as "Fat Pointers".

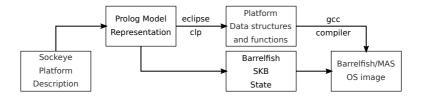

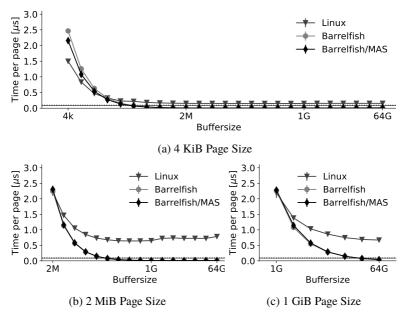

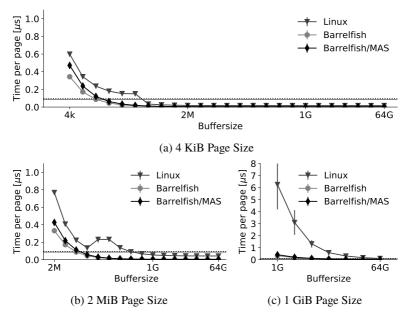

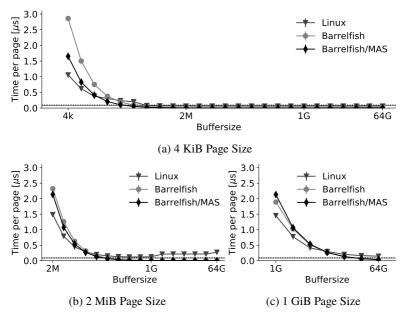

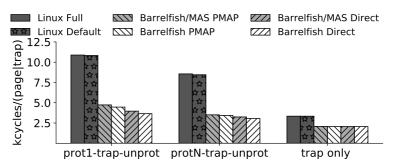

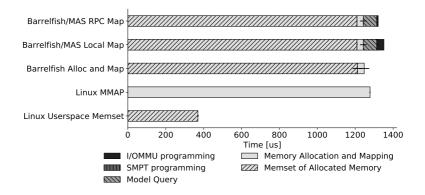

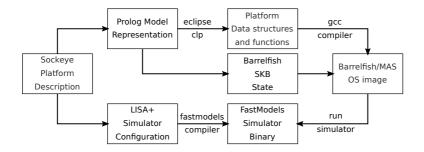

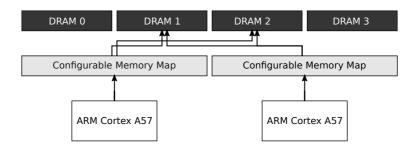

Memory accesses are sanitized against the size base and limit of the hardware capability (in the case of CHERI encoded in a "fat pointer") and any attempts of out-of-bounds accesses are blocked. CODOMs [Vil+14] tags every page in memory while using the instruction pointer as a capability that defines which page tags a program can access. Single address space operating systems use global address translations and enforce isolation by